הקדמה: מסורתית, אלמנטים שונים ברשת התקשורת עובדים בעומסי עבודה שונים על גבי ארכיטקטורות חומרה שונות, לדוגמא עיבוד החבילות (packets) על מעבדי רשת ותהליכי בקרה ויישומים על מעבדים בארכיטקטורה כללית (General Purpose Processors). התפרצותה של התעבורה הגלובלית העוברת ברשת – אשר מונעת מדרישת הלקוחות לתוכן עשיר להתקנים ניידים בכל זמן ובכל מקום, ומהצורך להוציא לשוק במהירות שירותים שיוצרים הכנסות – דוחפת את ספקי השירותים לבחון בתשומת לב את הוצאות ההון (CapEx) של הרשת העתידית. באותו זמן ממש, עלויות האנרגיה של תשתית הרשת נעות מעלה ומעלות את הוצאות התפעול (OpEx). כל אלו גורמים לספקי השירות לחפש פתרונות תקשורת ורישות שיספקו יחס אופטימלי של עלות מול ביצועים, בצד נצילות אנרגטית.

קיים מבחר של פלטפורמות שניתנות לשדרוג עבור מיזוג עומסי עבודה בארכיטקטורה יחידה, שמקטינות במידה ניכרת את מאמצי הפיתוח, את צריכת ההספק ואת זמן היציאה לשוק. כיום, אפשר למזג בארכיטקטורה יחידה אלמנטים ברשתות, שקודם לכן פעלו בעומסים שונים ובארכיטקטורות חומרה שונות, הודות ליתרונות הייחודים שמקנים הביצועים, והנובעים מטכנולוגיית ריבוי הליבות של ®Intel. יישומים, Control Plane ו-Packet Processing, פועלים כבר עתה במעבדי ובנוסף על אלו, ®Intel מציעה פקודות חדשות וספריות תוכנה מותאמות ובעלות אופטימיזציה לשיפור הביצועים של עיבוד האותות.

מיזוג עומסי עבודה מפחית את עלויות הפיתוח על ידי יצירת הזדמנויות רבות יותר למחזור (reuse) של תוכנה והפיכת שרשרת הכלים לפשוטה יותר, כזו שמשפרת את הנצילות, מקטינה את זמן ההכשרה, מקטינה את עלויות הרישוי ומאפשרת למתכנתים לעבוד על פונקצית מערכת כלשהי. יתר על כן, המעבר לארכיטקטורה יחידה מבטל את הצורך באינטגרציה ואימות ומאפשר להמנע מפיתוח חומרה, שכן יצרני הציוד יכולים להשתמש במעגלים מסחריים מהמדף (COTS) שמוצעים על ידי המגוון הרחב של שותפותיה של -®Intel. גם ספקי השירות יפיקו תועלת מהקטנת הוצאות התפעול הנובעת משיפור צריכת ההספק, ומהקטנת הוצאות תחזוקה הנלוות לניהול מערכות מורכבות מרובות ארכיטקטורות.

מאמר זה בא לתאר מערכות מרובות ביצועים, בעלות הספק נמוך, גמישות תכנונית וקיצור זמן יציאה לשוק, אשר ניתן להגיע אליה באמצעות מיזוג מודל 7 השכבות (OSI) לתוככי ארכיטקטורת אינטל.

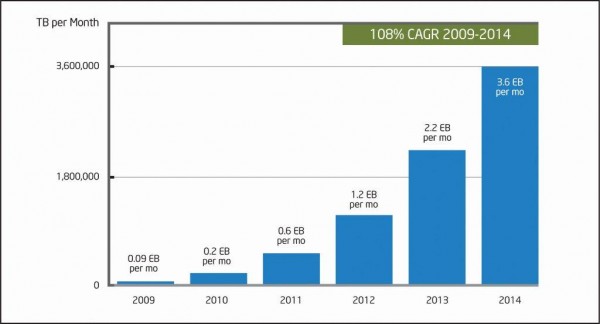

איור 1 התחזית של *Cisco לגבי תעבורת נתונים בהתקנים ניידים (המקור:Cisco*, 20101) 1 המקור: Cisco Visual Networking Index: Forecast and Methodology, 2009-2014, 9 בפברואר 2010 שאפשר למצוא אותו בכתובת: http://www.cisco.com/en/US/solutions/collateral/ns341/ns525/ns537/ns705/ns827/white_paper_c11-520862.html

עיקרי הביצועים במישור הנתונים

הצורך בביצועים טובים ל-Data Plane מתייחס לתחנות בסיס אלחוטיות (BTS), בקרי רשתות רדיו (RNC), נתבים ומתגים, ציוד אבטחה והזרמת נתונים ועוד. מערכות מבוססות סדרת C5500 של מעבדי ®Xeon של ®Intel יכולות להגיע לכ-20 מיליון חבילות בשנייה, ועל פי הצפוי, מעבד הדור הבא יתמוך ב-50 מיליון חבילות בשנייה. הפרטים הנוגעים לאבני הדרך של הביצועים הללו, מצויינים בחלקים הבאים של המאמר.

הצורך ברוחב פס נוסף

קשה להעריך את דרישות העתיד מהתקנים ניידים.

וידאו בהתקנים ניידים – שהוא פלח השוק שגדל במהירות הרבה ביותר – צפוי להקיף עד 66% של התעבורה הכוללת בשנת 2014. עד לשנה זו, תעבורת הנתונים בהתקנים ניידים עומדת להכפיל את עצמה מדי שנה, כך על פי התחזיות, ובשנת 20141 להגיע לפי 39 מאשר בשנת 2009.

כפי שניתן לראות באיור 1.

מיזוג עומסי עבודה

מיזוג עומסי עבודה

מנהלי פיתוח בוחנים בקפדנות אפשרויות לחלוקת מערכות (System Partitioning), כדי לבחור במרכיבי תוכנה וארכיטקטורות חומרה שעונים על דרישות המערכת בצורה הטובה ביותר. הנטייה היא לעקוב אחר שיטות מסורתיות, ולתכנן ארכיטקטורות חומרה מרובות שפועלות ברשת ומסבכות את תכנון החומרה והתוכנה. ארכיטקטורת מערכות זו מזמנת חוסר נצילות שנגרם, בין השאר, בגלל מחזור (שימוש חוזר) של רכיבים, אינטגרציה, מלאי ותאימות. החלופה היא להשתמש בארכיטקטורת מיחשוב יחידה, למיזוג עומסי העבודה של Control Plane וה-Data Plane של היישום, כולם פועלים בפלטפורמה מבוססת על מעבד בריבוי ליבות של ®Intel. גישה זו מעודדת את מחזור רכיבי החומרה והתוכנה, שבאופן משמעותי יכול להקטין את הוצאות הפיתוח של יצרני הציוד ולשפר את זמן היציאה שלהם לשוק, במקביל להקטנת הוצאות התחזוקה שמושתת על ספקי השירות.

כעת, המיזוג הפך לאפשרות מעשית, מפני שמשתמשים באותם מעבדי ®Intel שמשמשים בדרך של שגרה לעיבוד יישומים ול-Control Plane, עם אותו כוח מיחשוב שנדרש להפעלת תכניות חישוביות גדולות ומרובות נתונים. למשל, כפי שניתן לראות באיור 2, אפשר להפעיל שלושה עומסי עבודה על מעבד יחיד של ®Intel שפועל בריבוי ליבות, ולספק לרשתות WiMAX ו-eNodeB LTE את כל דרישות התפוקה של תחנת בסיס.

כדי לקחת את האינטגרציה צעד נוסף קדימה, אינטל מוסיפה יכולות למזג עומס עבודה רביעי – שכבה 1 (OSI), שכבת האיתות.

בתחנת הבסיס עצמה, יש בדרך כלל מספר משתנה של כרטיסים שמשתמשים בסיליקון לעיבוד כמו : CPUs , NPUs , DSPs , FPGAs , ASICs ו- ASSPs שכל אחד מהם מצריך תוכנה וקושחה (firmware) ייחודית.

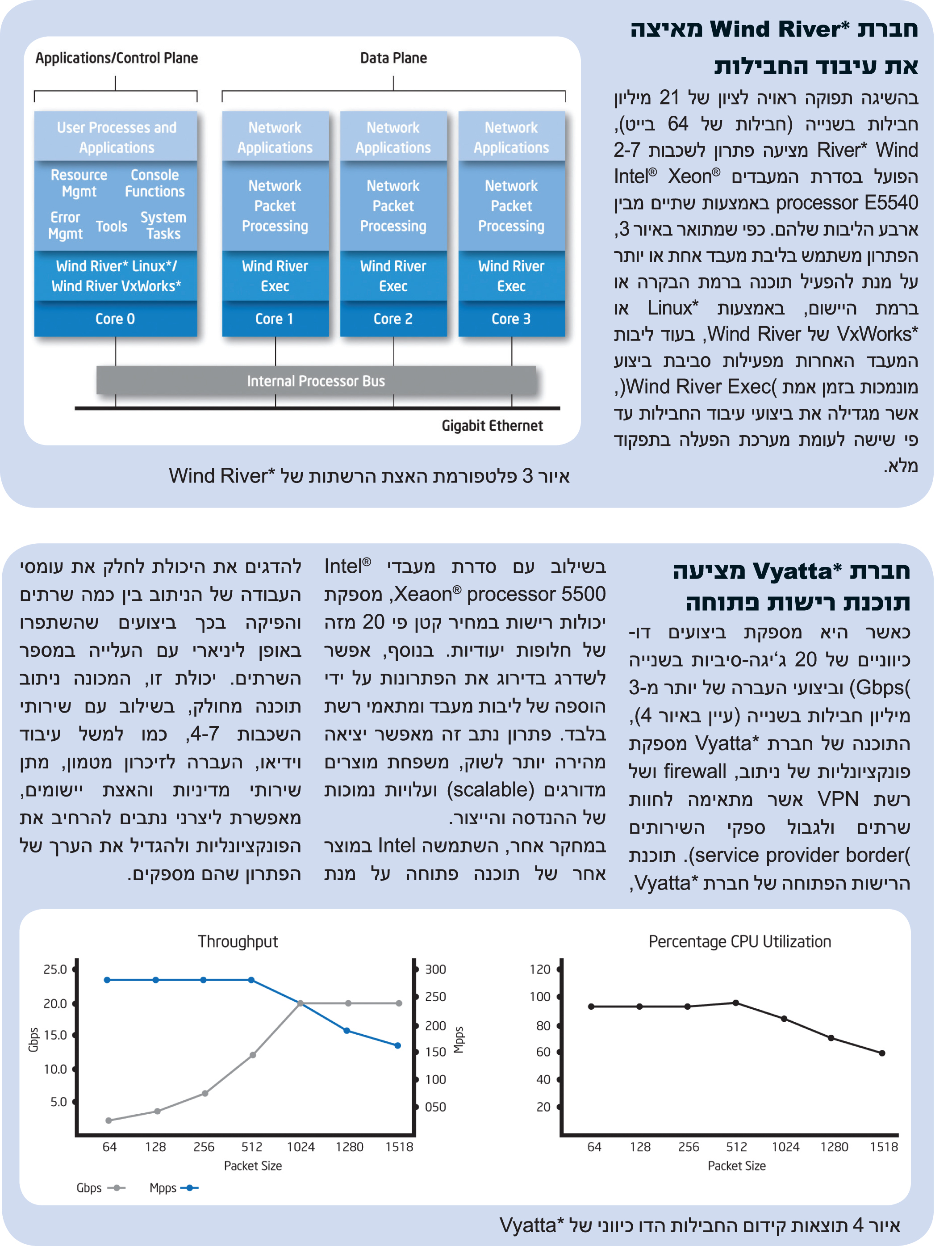

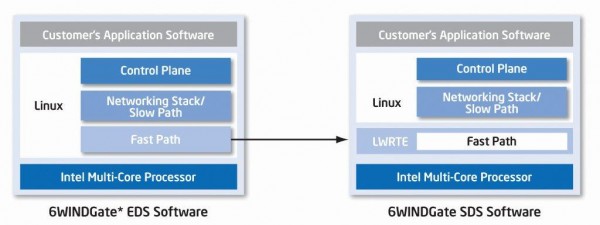

*6WIND מפשטת את ביצוע האופטימיזציה של מערכות כשהוא מגיע לביצועים של 246 מגה–חבילות בשנייה (Mpps) עם פרופיל EDS, הפתרון 6WINDGate הוא אחד הפתרונות המהירים ביותר והשלמים ביותר עבור מעבדי ®Intel לעיבוד חבילות בתוכנה עבור השכבות 2 עד 7. הוא מתוכנן במיוחד על מנת לפשט את פיתוח התוכנה ולהקטין למינימום את זמן תכנון המערכת באמצעות מישור בקרה מבוסס *Linux. הפרופיל של ערכת הפיתוח המורחבת 6WINDGate עונה על הספקטרום המלא של דרישות התכנון בריבוי ליבות, מליבה אחת לכל מספר של ליבות במעבד יחיד או בריבוי של מעבדים. כדי לשתף יע”מים (CPU), הנתיב המהיר ממומש כמודול של גרעין Linux בין מחסנית הרישות של Linux לבין מנהלי הממשק, ובכך גדלה התפוקה (throughput) במידה רבה מאחר שקוד Fast Path מועבר מליבה לליבה, ועוקף את רוב התקורה של מחסנית הגרעין של Linux. פרופיל “SDS” של 6WINDGATE יספק ביצועי עיבוד חבילות מרביים. בפלטפורמות של ריבוי ליבות המוגדרות בקונפיגורציה עם פרופיל SDS, הקוד של שכבת Fast Path פועל בערכת הפיתוח Intel Data Plane Development Kit בריבוי של ליבות, ומגדיל למקסימום את ביצועי עיבוד החבילות של המערכת, מאחר שרוב החבילות עוברות עיבוד בתוך שכבת Fast Path במקום שיועברו אל מחסנית Linux. מחסנית Linux עצמה מוגדרת בקונפיגורציה לפעולה רק באותו מספר ליבות שנדרש (בדרך כלל אחת), ומאפשרת בכך להקצות את יתר הליבות לשכבת Fast Path.*6WIND מפשטת את ביצוע האופטימיזציה של מערכות

יתרונות המיזוג בארכיטקטורה של ®Intel

הארכיטקטורה של ®Intel מציעה משפחה ניתנת לשדרוג, שכוללת מעבדים תואמי קוד שמכסים את כל דרישות הביצועים. יצרנים יכולים להפיק תועלת מהמבחר הרחב, ממעגלים מסחריים מהמדף, מרכיבי התוכנה ומכלי הפיתוח המובילים בתעשייה, אשר מקטינים את מאמצי התכנון, מפחיתים את עלויות הפתוח בחומרה ובתוכנה, ומפשטים את תהליך השגת האופטימיזציה במערכות ובפעולות, כאשר במקביל, הם מאפשרים למשאבים ההנדסיים להתמקד בפעולות בעלות ערך מוסף, לפי הפירוט הבא:

בתחום הקטנת עלויות פיתוח התוכנה

עבודה עם ערכת כלים אחת – מאפשרת לצפות בקלות בנקודות ההצטלבות של עומסי העבודה ולזהות צווארי בקבוק.

הקצאת מתכנתים לכל פונקציה של המערכת – מאפשרת להגדיל את גמישות ניהול הפרויקט, מפני שלא קיימים מחסומים מבניים.

מינוף באמצעות קהילת תוכנה גדולה – שכוללת קוד מקור פתוח, חבילות תמיכה במעגלים (BSP) ומנהלי התקנים (Device Drivers), ושגורמת להקטנת כמות הקוד שיש לכתוב.

הגנה על ההשקעות בתוכנה – על ידי השימוש במעבדים בארכיטקטורה של ®Intel בעלי תאימות תוכנה אמיתית לאחור.

בתחום הקטנת עלויות פיתוח החומרה

תכנון פחות מעגלים – על ידי אימוץ פתרונות מסחריים מהמדף (COTS), אשר גורם להקטנה עד למינימום של מאמץ התכנון ומאפשר שימוש בטכנולוגיות המעבדים המתקדמות ביותר.

מניעת בעיות אינטגרציה ותאימות – מניעה של בעיות שנוצרות מעירוב של ארכיטקטורות חומרה מרובות, גורמת לחיסכון בזמן.

תכנון פלטפורמה יחידה לריבוי יישומים – פלטפורמה יחידה, מפני שהיא יכולה להריץ מגוון תוכנות יישומים.

בתחום אופטימיזציה של מערכות ופעולות

אופטימיזציה קלה למערכות – על ידי חציצה מחדש באמצעות תכנה בליבות המעבד והעברת כוח המחשוב לשימוש הייחודי שבו הוא נדרש.

יצירה פשוטה של דירוג ביצועי המערכת – על ידי הוספת ליבות מעבד, במטרה להגיע ליעדים שונים של ביצועים מול עלויות, מבלי שתהיה לכך השפעה על בסיס הקוד.

הגדלת פונקציונליות המערכת – באמצעות מיזוג יישומים מרובים ביחידת ציוד יחידה (למשל תקני רדיו רבים – LTE, WiMAX) שייתן ערך מוסף של הפתרון.

הקטנת עלויות התפעול – כתוצאה מהצורך בפחות מעגלים בעת ההרכבה, אנו חוסכים במלאי , תחזוקה , ותמיכה.

הנתיב ל-Packets Processing מהיר יותר

יצירת סביבה, שבה מעבד רב תכליתי בריבוי ליבות יכול להגיע לתפוקה של Packets Processing שדומה למעבד רשת (NPU), אינה משימה קלה. מזה כמה שנים, ®Intel מפתחת את היכולת הזו, ומחויבת לספק Packets Processing מהיר יותר, עם יציאתם לשוק של מוצרים חדשים. ההתפתחות לכיוון של ביצועים מהירים יותר Data Plane, עם תפוקה שמתוכננת לעלות על 50 מיליון חבילות בשנייה (Mpps) בדור הבא של המעבדים, מתוארת באיור 4. הסעיפים הבאים מפרטים את השיפורים שנעשו לאורך הדרך.

5 מגה–חבילות בשנייה (3.4 ג’יגה–סיביות בשנייה) סדרת 5400 של מעבדי ®Xeon של ®Intel :

התוצאות מבוססות על מחסנית רשת סטנדרטית ב-Linux עם התאמות בודדות:

מצב פסיקת MSI מאופשר

התקני חומרה של המעבד להבאה מראש (prefetcher) מהזיכרון אינם מאופשרים

מתאם השרת PRO/1000GT Quad Port Server Adapter של ®Intel משולב עם מנהל התקן מאופשר NAPI

16 מגה–חבילות בשניה (10.8 ג’יגה-סיביות בשניה) סדרת C5500 של מעבדי ®Xeon של ® Intel:

התוצאות מבוססות על תוכנת קידום מורחבת ב-L3 עם השינויים הבאים:

החלפת החלקים של Linux IP ושל מחסנית הקידום בתוכנה מותאמת אישית לטיפול בחבילות

ביטול כמה צווארי בקבוק במחסנית Linux IP הנגרמים בשל נעילות סיבוב (spinlock) וכתוצאה מחוסר תמיכה בריבוי תורים

יצירת מעקף לגרעין Linux לצורך עיבוד חבילת (למשל חיפוש ועיבוד זרימה)

מימוש ממשק API חדש (NAPI) ומצב פסיקה בתוכנה אשר משתמש בתשאול (polling), תחליף לפסיקות בחומרה

35.7 מגה–חבילות בשניה (24 ג’יגה–סיביות בשניה) סדרת E5540 של מעבדי ®Xeon של ®Intel

התוצאות מבוססות על אב טיפוס של ערכת פיתוח Data Plane של ®Intel, עם התכונות הבאות:

סביבה קלת משקל לזמן פעולה, המציעה מודל פעולה עד השלמה בתקורה נמוכה עם עיבוד חבילות בעל ביצועים גבוהים במישור עיבוד הנתונים

ספריות עבור זיכרון, עמידה בתור וניהול זיכרון זמני, אשר מספקות פונקציות תוכנה באופטימיזציה מרובה להשגת ביצועים יוצאי דופן.

שכבת הפשטה סביבתית שיכולה להשתנות בין מודלים שונים של פרישה (למשל בחומרה בלבד ומרחב המשתמש של Linux)

יותר מ–50 מגה–חבילות בשניה – הדור הבא של מעבדי ®Xeon של ®Intel:

התוצאות המתוכננות מבוססות על ארכיטקטורת מיקרו חדשה ועל האינטגרציה של ערכת הפיתוח למישור הנתונים של ®Intel במחסניות רשת מסחריות מבית היוצר של מפתחי צד שלישי. חברות כגון *WIND6 ו-*WIND RIVER.

ערכת הפיתוח Data Plane של ®Intel, המתוארת באיור 5, היא חבילת תוכנה לשימוש ברשיון BSD, שנמצאת זמינה בשוק החל מהמחצית השנייה של שנת 2010. ערכת הפיתוח אינה כוללת את מודולי התוכנה המופיעים במחצית העליונה של האיור (אבטחה, ניתוב, ומערכות אלחוטיות); עם זאת, אפשר להשיג אותם מיצרני תוכנה. ערכת הפיתוח ל-Data Plane מספקת נקודת התחלה טובה למפתחי מערכות אצל יצרני ציוד OEM, ואצל ספקי תוכנה עצמאיים (ISV) ופתרונות מסחריים עם כל התכונות זמינים בשוק.

הקטנת הוצאות התפעול עם מעבדי ®Intel בעלי נצילות ההספק הגבוהה

אנשי פיתוח המשתמשים במוצרי ®Intel יכולים לסמוך על כך שיקבלו את הטכנולוגיה המתקדמת ביותר עבור מוצרים עתידיים, לאורך ציר זמן אמין וניתן לחיזוי. ציר הזמן עוקב אחרי מודל “טיק–טוק” (Tick–Tock) של ®Intel להשגת חדשנות מתמשכת המתבססת על אספקת טכנולוגיית תהליך סיליקון חדשה (טיק) בשנה אחת וארכיטקטורת מיקרו של מעבדים חדשה לחלוטין (טוק), בשנה שלאחר מכן.

התוצאות באות לידי ביטוי במוצרים היוצאים לשוק מבית היוצר של חברת RADISYS, ספק מוביל של פתרונות חומרה ותכנה לשוק התקשורת. איור 6 מראה את התפתחות ביצועי מספרים שלמים (INTEGER) ומספרי נקודה צפה (FLOATING POINT) במשך ארבעה דורות של כרטיסי מחשוב יחיד. הבולט מבינהם הוא כרטיס המבוסס מעבד 5518L XEON.

המעבד ®Xeon של Intel® – L5518 – מציע שיפורים אוטומטיים בנצילות אנרגיה, ומספק למשתמשים יכולת טובה יותר לבקרה של צריכת האנרגיה. יכולת זו כוללת רמת הספק של מעבד במצב סרק המגיעה ל-10 ואט בלבד, ומאפשרת הקטנת הצריכה ב-50% במערכת שפועלת במצב סרק, בהשוואה למערכות מהדור הקודם. טרנזיסטורי power gate, המבוססים על טכנולוגיית השערים הייחודית high-k metal – של ®Intel, מאפשר כיבוי עצמאי של אותן הליבות הנמצאות במצב סרק.

המעבד תומך בעד 15 מצבי פעולה אוטומטיים, תכונה שמקדמת את ניהול ההספק החכם לרמה חדשה. מצבים אלו משפרים באופן משמעותי את הגמישות הקיימת בניהול הספקים, על ידי התאמה של צריכת ההספק במערכת, בהתבסס על התפוקה בזמן אמת, ומבלי לגרוע מן הביצועים. כאשר ספקי השירות מתמקדים בעלויות לספקי החשמל, המודל טיק – טוק של ®Intel ממשיך לענות על הצורך בנצילות אנרגיה טובה יותר.

שילוב ערוץ PCI Express במעבד

שילוב ערוץ PCI Express במעבד

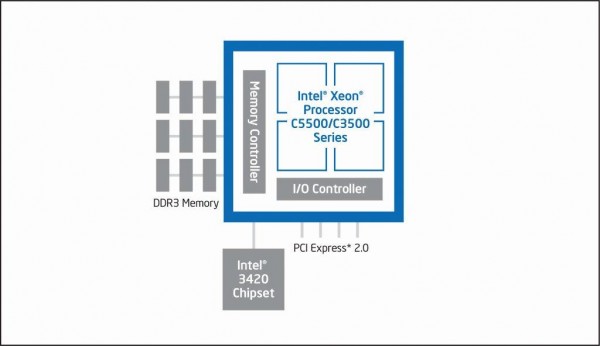

במקום שבו יש חשיבות לחיסכון במקום על המעגל ולהורדת צריכת ההספק, אפשר להשתמש בסדרה C5500/C3500 של מעבדי ®Xeon של ®Intel המבוססת על ארכיטקטורת המיקרו של ®Intel בעלת שם הקוד Nehalem, אשר מספקת את שניהם. ערוצי PCI Express, אשר נמצאים בדרך כלל ברכזות I/O, משולבים כיום בתוך מעבדים ומבטלים את הצורך בשבב נפרד של רכזת I/O. במצב זה המספר הכולל של השבבים מוקטן באחד ונוצר חיסכון בהספק הכולל של המערכת, אשר הופכים את הפלטפורמה למתאימה במיוחד עבור יישומים שבהם יש מגבלות חום ומקום.

הסדרה החדשה הזו מציעה יכולת שדרוג ללא תקדים, עם אפשרויות מליבה יחידה ועד ארבע ליבות בטווח של “הספק תכנון חום” (TDP) שבין 23 ואט לבין 85 ואט. את מעבדי הסדרה אפשר לקבל בקונפיגורציה של מעבד יחיד (איור 7) או בקונפיגורציה של מעבד כפול עם חיבור פנימי מסוג QuickPath של ®Intel אשר מספק גמישות תכנונית גדולה אף יותר.

הקטנת המורכבות והפחתת עלויות תכנון

ככל שספקי השירות מוסיפים קיבולת לרשתות על מנת להשביע את הדרישה המתפרצת, בעתיד הקרוב, הם יתמקדו בהוצאות הון (CapEx) ובהוצאות תפעול (OpEx). בתגובה לכך, יצרני הציוד שיקטינו את הוצאות הפיתוח שלהם, יוכלו להעביר חלק מהחיסכון ליצירה של יתרונות תחרותיים בשוק. הביצועים יוצאי הדופן של מעבדי ®Intel בעלי ריבוי ליבות יוצרים כיום הזדמנות חדשה: מיזוג של עומסי עבודה ברשתות מרובות אל תוך ארכיטקטורה יחידה. גישה מבנית זו מקטינה את מאמצי ההנדסה של החומרה והתוכנה, תוך קבלת יתרון מהגידול המתמיד בביצועים להספק של הפלטפורמות מבוססות המעבדים של ®Intel. עבור תכנונים שבהם משתמשים במבחר של רכיבי NPU, DSP, FPGA ו-ASIC ייתכן שעתה הוא הזמן לנקוט בגישה חדשה שמשפרת את זמן היציאה לשוק ומפחיתה את המורכבות ללא הקרבת הביצועים.