השימוש בתקן ™OpenCL של קבוצת Khronos על FPGA יכול להציע ביצועים גבוהים יותר משמעותית והספק הרבה יותר נמוך משקיים כיום בארכיטקטורות חומרה דוגמת CPUs ,graphics processing units) GPUs) ויחידות עיבוד אותות דיגיטלי (DSP-(digital signal processingl. בנוסף, למערכת הטרוגנית מבוססת-FPGA המשתמשת בתקן OpenCL יתרון משמעותי בזמן לשיווק בהשוואה לפיתוח FPGA רגיל המשתמש בשפות תאור חומרה ברמה נמוכה יותר (HDLs) דוגמת Verilog או VHDL.

השימוש בתקן ™OpenCL של קבוצת Khronos על FPGA יכול להציע ביצועים גבוהים יותר משמעותית והספק הרבה יותר נמוך משקיים כיום בארכיטקטורות חומרה דוגמת CPUs ,graphics processing units) GPUs) ויחידות עיבוד אותות דיגיטלי (DSP-(digital signal processingl. בנוסף, למערכת הטרוגנית מבוססת-FPGA המשתמשת בתקן OpenCL יתרון משמעותי בזמן לשיווק בהשוואה לפיתוח FPGA רגיל המשתמש בשפות תאור חומרה ברמה נמוכה יותר (HDLs) דוגמת Verilog או VHDL.

מבוא

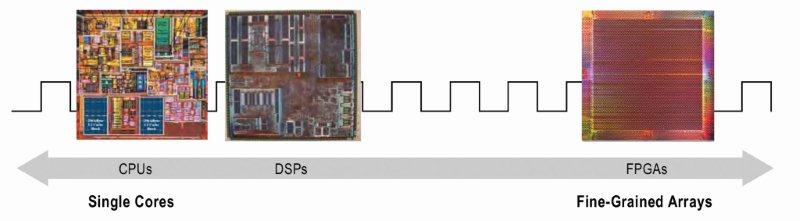

העידן ההתחלתי של טכנולוגיות מיתכנתות כלל שני קצוות שונים של יכולת תכנון. כמתואר באיור 1, קצה אחד הוצג על-ידי יחידות CPU חד-ליבתיות ועיבוד נתונים דיגיטלי (DSP). התקנים אלה ניתן היה לתכנת תוך שימוש בתוכנה המורכבת מרשימת הוראות שיש לבצע. הוראות אלו נוצרו בצורה שהייתה סדרתית כמושג כלפי המתכנת אם כי מעבד מתקדם יכול היה לרשום הוראות להפקת מקבילות ברמת-ההוראות מתוכניות סדרתיות אלו בזמן ריצת התכנית. בניגוד, הקצה השני של טכנולוגיה מיתכנתת הוצג על-ידי ה-FPGA. התקנים אלה מתוכנתים על-ידי יצירת מעגלי חומרה הניתנים לעיצוב, המבצעים את ההוראות כולן במקביל. מתכנן המשתמש ב-FPGA יוצר במהות יישום מקבילי בעל גרגירים עדינים. במשך שנים רבות, קצוות אלה התקיימו ביחד עם כל סוג של יכולת תכנות המבוצע על אזורי יישום שונים. אולם, מגמות חדשות של הכפלה (scaling) בטכנולוגיה העדיפו טכנולוגיות שהן מיתכנתות ומקביליות.

עם גבור הצורך בביצועים, התקנים מיתכנתים-בתוכנה המבצעים תכנית סדרתית הסתמכו במידה עולה על שתי מגמות-יסוד כדי לשפר את ביצועיהם. הראשונה הייתה הכפלת תדר הפעולה בשעה שדורות המעבדים צמחו. בשל מגוון סיבות, אנחנו לא יכולים יותר להמשיך במגמת ההכפלה של מתח הפעולה לנמוך יותר ולהעלות את תדר הפעולה תוך שמירה על צפיפויות הספק סבירות. תופעה זו הידועה כ”חומת ההספק” גורמת לשינויים משמעותיים בארכיטקטורה של כל סוגי ההתקנים המיתכנתים.

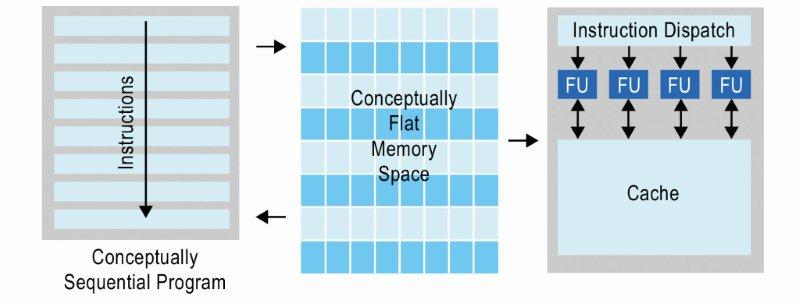

המגמה השנייה עליה התבססו התקנים מיתכנתים בתוכנה הייתה ההופעה של חומרה מורכבת אשר תפיק מקבילוּת ברמת-ההוראה מתכניות סדירות. כמתואר באיור 2, ארכיטקטורה חד-ליבתית הייתה מביאה לזרם הוראות ומבצעת אותן על התקנן שעשוי להיות בעל יחידות פונקציונליות מרובות. חלק משמעותי של חומרת המעבד צריך להיות מוקדש להוצאת המקבילוּת בצורה דינמית מהקוד הסדרתי.

בנוסף, החומרה שאפה לפצות על כמיסות (latency) הזיכרון. ככלל, מתכנתים יוצרים תכניות מבלי להתחשב בהירארכיית הזיכרון בהסתרת, כאילו שהיה רק זיכרון אחד גדול, חלק, מהיר בצורה שווה. בניגוד, המעבד צריך לטפל במציאות הפיסיקלית של חיבורי כמיסות-גבוהה ורוחב-פס מוגבל לזיכרון החיצוני. כדי לשמור על היחידות הפונקציונליות להיות מוזנות עם נתונים, המעבד צריך גם לשנות מראש נתונים מהזיכרון החיצוני לתוך זיכרון-מטמון על-השבב כך שהנתונים הם הרבה יותר קרובים לאזור בו מבוצע החישוב. אחרי הרבה עשורים של שיפורי ביצועים תוך שימוש בטכניקות אלה, היו חזרות קטֵנות בהרבה מסוגים אלה של ארכיטקטורות.

בהתחשב ביתרונות הקטֵנים של שתי מגמות אלו בארכיטקטורות של מעבד רגיל, אנחנו מתחילים לגלות שהספקטרום של התקנים המיתכנתים-בתוכנה מתפתח משמעותית, כמתואר באיור 3. הדגש נע מההוצאה האוטומטית של מקבילות ברמת-ההוראה בזמן התהליך אל הזיהוי המפורש של המקבילות ברמת ההליך בזמן הקידוד. התקנים מרובי-ליבה המקבילים בצורה גבוהה מתחילים להתמזג עם המגמה הכללית של הכללת מעבדים מרובים פשוטים יותר כאשר יותר טרנזיסטורים מוקדשים לחישוב מאשר להטמנה והוצאה של המקבילות. התקנים אלה נעים מ-CPUs מרובי-ליבה, להם בד”כ 2, 4 או 8 ליבות, ל-GPUs המורכבים ממאות ליבות פשוטות הממוטבות עבור חישוב בנתונים מקבילים. כדי להשיג ביצועים גבוהים על התקנים מרובי-ליבה אלה, המתכנת צריך לקודד בצורה מפורשת את היישומים שלו בצורה מקבילה. לכל קוד צריך להקצות עבודה באופן כזה שכל הליבות יוכלו לשתף פעולה לביצוע חישוב מסוים. זהו גם בדיוק מה שמתכנני FPGA עושים כדי ליצור את ארכיטקטורות המערכת בעלות רמה גבוהה שלהם.

בהתחשב בצורך ליצור תכניות מקבילות עבור עידן מרובי-הליבות המגיח, הוכר שקיימים צרכים של מודל תקני עבור ייצור תכניות אשר יבצע לאורך כל ההתקנים השונים הללו. היעדר תקן התואם את כל הטכנולוגיות המיתכנתות האלה הציק למתכנתים. בקיץ 2008, Apple הגישה תכנית של מפרט מקדים עבור OpenCL לקבוצת Khronos במאמץ ליצור תקן תכנות מקבילי חוצה-פלטפורמה. קבוצת Khronos מורכבת מתאגיד של גורמי תעשייה כגון Apple, IBM, Intel, AMD, NVIDIA, Altera ורבים אחרים. קבוצה זו הייתה אחראית להגדרת מפרטי OpenCL 1.0, 1.1 ו-1.2. תקן ה-OpenCL מאפשר מימוש של אלגוריתמים מקבילים שניתן להעביר מפלטפורמה לפלטפורמה בעזרת קידוד מזערי. השפה מבוססת על שפת התכנות C ומכילה הרחבות המאפשרות פירוט המקבילות.

בנוסף ליצירת מודל נייד, תקן ה-OpenCL מציע באופן טבעי את היכולת לתאר אלגוריתמים מקבילים שיש לממש על FPGAs, בדרגת הפשטה ברמה הרבה יותר גבוהה מאשר שפות תאור חומרה

דוגמת VHDL או Verilog. אם כי קיימים כלי סנתוז ברמה גבוהה רבים לשם השגת רמה גבוהה יותר זו של הפשטה, הם סבלו כולם מאותה הבעיה היסודית. כלים אלה היו שואפים ליטול תכנית C סדרתית וליצור מימוש ב- HDL מקבילי. הקושי היה לא כל כך ביצירת HDL אלא יותר בהוצאת המקבילות ברמה של הליך המאפשר למימוש ה-FPGA להשיג ביצועים גבוהים. עם היותם ה-FPGAs בקצה המרוחק של הספקטרום המקבילי, כל כשל בהפקת מקבילות מרבי הוא יותר מדכא מאשר בהתקנים אחרים. תקן ה-OpenCL פוטר רבות מבעיות אלו באפשרו לתכנת לפרט ולבקר בצורה ברורה את המקבילות. תקן ה-OpenCL תואם בצורה טבעית יותר את האופי המקבילי ביותר של ה-FPGAs מאשר תכניות סידוריות המתוארות ב-C טהור.

הסבר קצר על

תקן ה-OpenCL

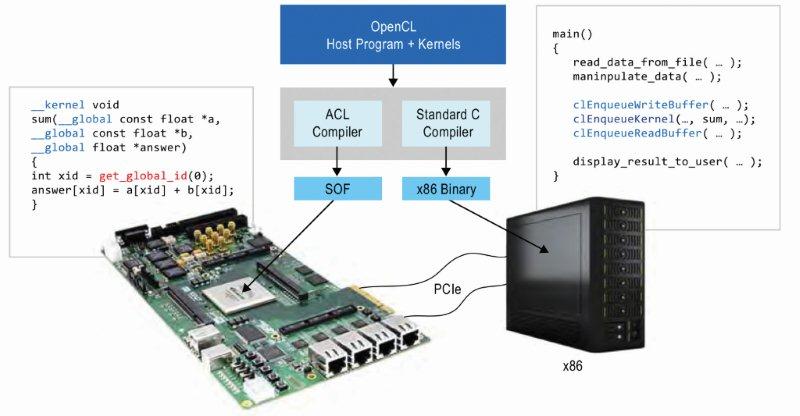

יישומי ה-OpenCL מורכבים משני חלקים. תכנית המארח OpenCL היא רוטינת תוכנה טהורה הכתובה ב-C/C++ תקנית, הרצה על כל סוג של מיקרו-מעבד. המעבד הזה יכול להיות, לדוגמה, מעבד תוכנה מובנה בתוך FPGA, מעבד ARM קשיח, או מעבד x86 חיצוני, כמתואר באיור 4.

בנקודה מסוימת במהלך ביצוע רוטינה זו של תוכנת מארח, סביר כי תהיה פונקציה היקרה במחשוב והיכולה ליהנות מהתאוצה המקבילה הגבוהה על התקן יותר מקביל: CPU, GPU, FPGA וכד’. פונקציה זו שיש להאיץ מכונה OpenCL kernel. קרנלים אלה כתובים ב-C תקני; אולם הם נושאים הערות הנועדות לפרט מקבילות והירארכיית זיכרון. הדוגמה המוצגת באיור 5 מבצעת את החיבור הווקטורי של שני מערכים, a ו-b, תוך רישום התוצאות בחזרה אל מערך תשובה במוצא. תהליכים מקבילים פועלים על כל מרכיב של הווקטור, ומאפשרים לתוצאה להיות מחושבת הרבה יותר מהר כאשר היא מואצת על-ידי התקן המציע כמויות גדולות של מקבילות דקת-גרעין דוגמת FPGA. לתכנית המארח יש גישה לממשקי תכנות יישום OpenCL תקניים (APIs) המאפשרים לנתונים להיות מועברים אל ה-FPGA, תוך קישור אל הקרנל על ה-FPGA והעברת נתוני התוצאה בחזרה.

פרטים נוספים על תקן ה-OpenCL ניתן למצוא באתר קבוצת Khronos.

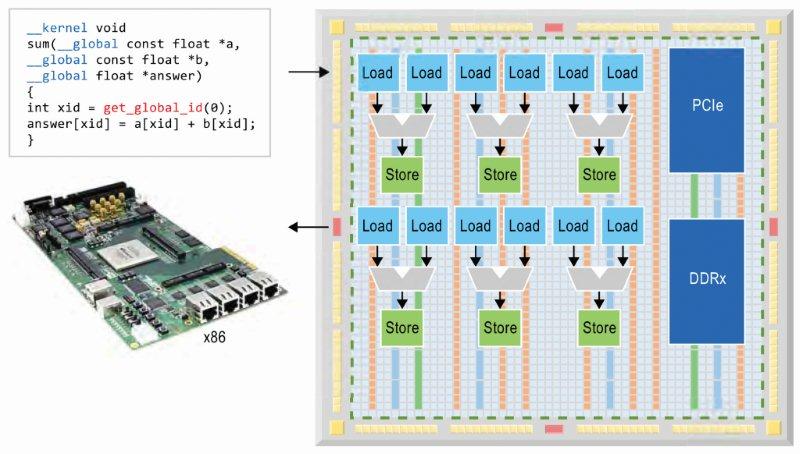

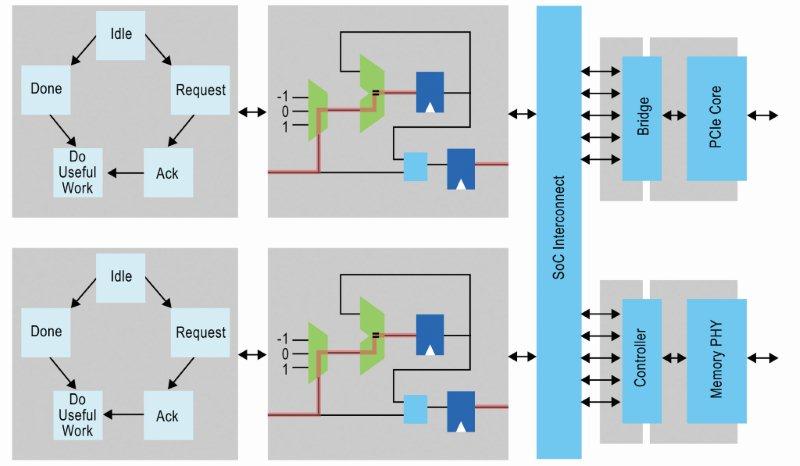

שלא כמו ב-CPUs ו-GPUs, בהם ניתן לבצע הליכים מקבילים על ליבות שונות, FPGAs מציעים אסטרטגיה שונה. פונקציות קרנל ניתן להפוך למעגלי חומרה בחפיפה עמוקה שהם מטבעם מרובי-תהליכים תוך שימוש במקבילות החפיפה. כל אחת מחפיפות אלו ניתן להעתיק הרבה פעמים כדי לספק יותר מקבילות מאשר אפשרי כחפיפה יחידה. כמתואר באיור 5, ניתן לממש את קרנל הוספת הווקטור על-ידי יצירת דירוג של יחידות פונקציונליות כדי לממש כל פעולה בתיאור ה-OpenCL ולהעתיקה כדי לענות לדרישות התפוקה והכמיסות של היישום. אם כי הוצגה כאן הצגה פשוטה, כל יחידה פונקציונלית ניתן לחפוף בצורה מעמיקה כדי להבטיח שתדר הפעולה של המעגל הנוצר הוא די גבוה. בנוסף, המהדר (compiler) יכול ליצור את המעגלים לשם ניהול התקשורת אל המערכת החיצונית. בדוגמה זו, בקרי DDRx ו-PHYs מחוברים לקרנל כדי לאפשר לו גישה למערכים מחוץ-לשבב גדולים ביעילות גבוהה. בדומה, IP של מופעל אוטומטית ומחובר לקרנל כך שמארח x86 יוכל לתקשר עם מאיץ ה-FPGA דרך ה-APIs של OpenCL.

יתרונות במימוש תקן ה-OpenCL על FPGA

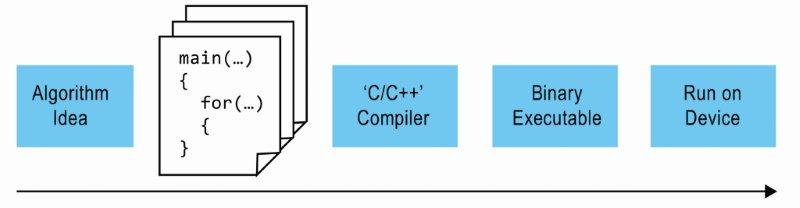

יצירת תכנונים עבור FPGA תוך שימוש בתאור ה-OpenCL מכילה מספר יתרונות בהשוואה לשיטות המסורתיות המבוססות על תכנון HDL. המשמעותי ביותר מהם מוצג באיור 6. פיתוח התקנים מיתכנתים בתוכנה עוקב אחרי גיבוש הרעיון, לאחר מכן קידוד האלגוריתם בשפה גבוהה דוגמת C, ולבסוף שימוש במהדר אוטומטי כדי ליצור את תזרים הפקודות.

גישה זו ניתנת להשוואה עם שיטות התכנון המבוססות על FPGA. כאן, הרבה מהעומס מוטל על המתכנן כדי ליצור תיאורים מחזור-אחר-מחזור, של חומרה המשמשים למימוש האלגוריתם שלהם. התזרים המסורתי המוצג באיור 7, כולל יצירת נתיבי נתונים, מכונות מצב לשם בקרה על נתיבי נתונים אלה, התחברות לליבות IP ברמה נמוכה תוך שימוש בכלים ברמת המערכת (דוגמת SOPC Builder, Platform Studio), וטיפול בבעיות סגירת התזמון מאחר שממשקים חיצוניים יוצרים אילוצים קבועים שיש למלא אחריהם. המטרה של מהדר OpenCL היא לבצע את כל השלבים הללו אוטומטית עבור המתכננים, ולהרשות להם להתמקד בהגדרת האלגוריתמים שלהם במקום להתמקד בפרטים המשעממים של תכנון חומרה. תכנון בדרך זו מאפשר למתכנן לעבור בקלות אל FPGAs חדשים המציעים ביצועים טובים יותר ויכולות גבוהות יותר משום שמהדר ה-OpenCL יהפוך תאור ברמה גבוהה זה למסלולים המנצלים את ה-FPGAs החדשים.

ניתוח אירוע:

שיטת Monte Carlo Black-Scholes

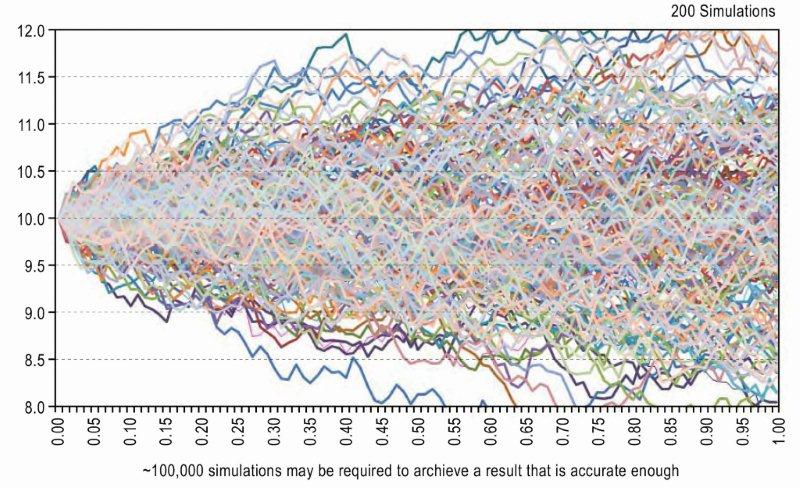

אחד סעיפים החשובים ביותר למדידת ביצועים בשווקים הכלכליים הוא החישוב של מחירי אופציות באמצעות שיטת Monte Carlo Black-Scholes. הטכניקה מבוססת על ניהול הדמייה אקראית של מחיר המנייה היסודי ועריכת ממוצע של התמורה הצפויה דרך מיליוני נתיבים שונים. דוגמה של הדמיות אלו מוצגת גראפית באיור 8.

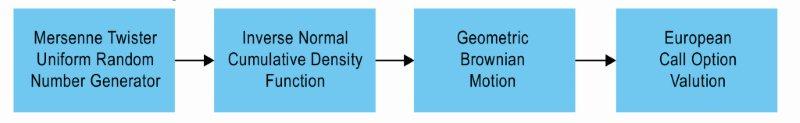

המבנה בעל הרמה הגבוהה של האלגוריתם המבצע חישוב זה מוצג באיור 9. מחולל מספרים אקראיים של Mersenne משמש תחילה כדי ליצור ערכים מפולגים באופן שווה. רצף זה של מספרים אקראיים מוזן אל פונקציית צפיפות Inverse Normal Cumulative כדי ליצור רצף בעל פילוג נורמלי. מספרים אקראיים אלה משמשים לאחר מכן להדמיית תנועת מחירי השוק תוך שימוש בתנועה Geometric Brownian. בסוף כל נתיב הדמייה, תשלום האופציה הנבחרת נרשם וממוצע כדי ליצור ערך חזוי עבור התשלום (סילוק החוב). ניתן לממש את האלגוריתם המלא בכ-300 שורות של קוד OpenCL שניתן להעבירו מ-FPGA אל CPU ו-GPU.

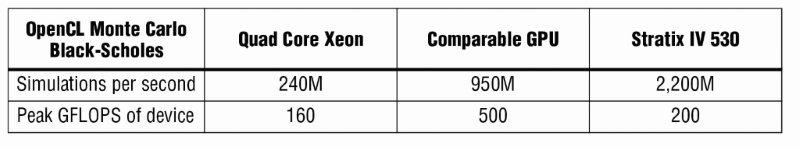

שימוש במערכת OpenCL שפותחה עבור ה-FPGAs של ®Altera נותן תוצאות מצוינות, כמתואר בטבלה 1. בניגוד ל-GPU דומה, מערכת ה-OpenCL המכוונת ל-Stratix® IV FPGA EP4SGX530 עוברת על התפוקה של ה-CPU ו-GPU כאחד. בנוסף לתפוקה הגדולה יותר, פתרונות ה-FPGA צורכים, לפי הערכות מתונות, חמישית מהספק של GPUs דומים כאשר הם מבצעים את אותו הקוד. צירוף זה של מהירות ויעילות הספק מפחית את דרישות האנרגיה עבור יישומים עשירים במחשוב.

סיכום

שימוש בתקן OpenCL ב-FPGA עשוי להציע ביצועים גבוהים יותר בהספק הרבה יותר נמוך מאשר קיים כיום בארכיטקטורות חומרה (CPU, GPUs וכד’). בנוסף, למערכת הטרוגנית מבוססת- המשתמשת בתקן OpenCL יש יתרון משמעותי בזמן לשיווק בהשוואה לפיתוח FPGA המשתמש בשפות תאור חומרה ברמה נמוכה יותר (HDLs) כגון Verilog או VHDL. Altera הצטרפה לקבוצת Khronos ב-2010 והיא תורמת פעילה לתקן.

הכתבה נמסרה באדיבות חברת איסטרוניקס

Deshanand Singh, Altera Corporation