מאת: Haim Cohen, Freescale Semiconductor Israel. מהנדסים רבים שהתעסקו אי פעם עם מודולי זיכרון מסוג DDR SDRAM, ככל הנראה, הסתקרנו מפרמטרי התזמון השונים של זיכרון DRAM. מאמר זה מסביר את הפרמטרים השונים של התזמון ואת השפעתם על ביצועי DRAM.

מאת: Haim Cohen, Freescale Semiconductor Israel. מהנדסים רבים שהתעסקו אי פעם עם מודולי זיכרון מסוג DDR SDRAM, ככל הנראה, הסתקרנו מפרמטרי התזמון השונים של זיכרון DRAM. מאמר זה מסביר את הפרמטרים השונים של התזמון ואת השפעתם על ביצועי DRAM.

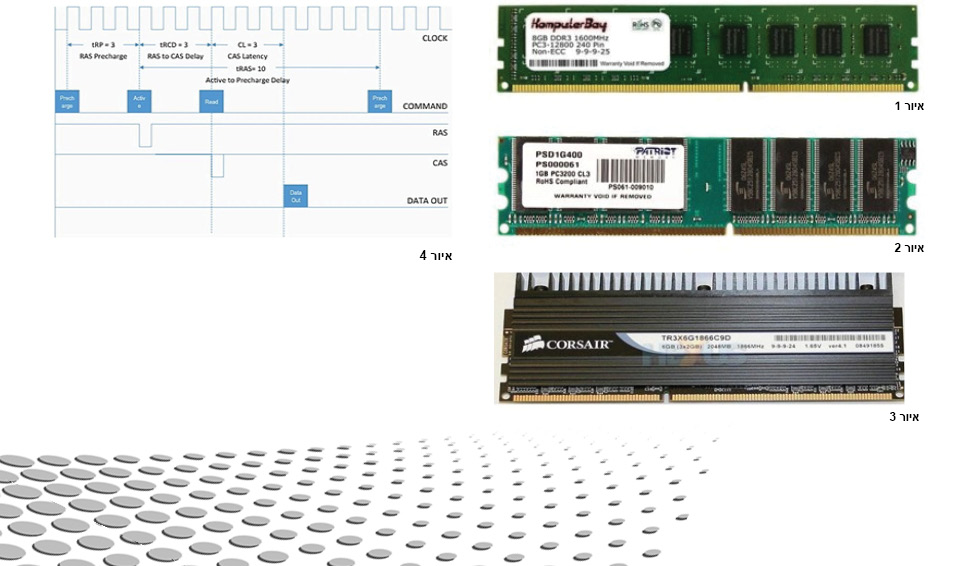

בתור התחלה, נבין קודם לכן את הדרך שבה מדרגים או מסווגים את זיכרונות DDR השונים. אם אנו מעונינים לרכוש מודול DDR מהשוק, עלינו לקחת בחשבון פרמטרים רבים, בהם נכללים גודל, מהירות, מפרט טכני של תזמונים, מותג וכיו”ב. לכן, יש לנו אפשרויות רבות שמהן אנו יכולים לבחור. על מנת להבין בצורה טובה יותר את הדירוגים האלו, נבחן תחילה כיצד הם מוצגים בפני הקונים. לפנינו תמונה של מודול זיכרון DDR SDRAM.

כפי שניתן לראות באיור 1, הקריאה המוצגת במודול היא DDR3–1600MHz, PC3-12800. אם כן, מה המשמעות של הקוד הזה? ב-DDRx-yyyy ה-x מציין את הדור של הטכנולוגיה (למשל: DDR,

DDR3, DDR) ו-“yyyy” מציין את קצב אות השעון של DDR או באופן נכון יותר את קצב הנתונים. כפי שהשם מרמז, DDR (קצב נתונים כפול – Double Data Rate) מעביר שני נתחי נתונים בכל מחזור אות שעון, ולכן מגיע לפי שניים ביצועים, בהשוואה לזיכרון שאין לו תכונה זו. לכן, מודולי DDR מדורגים לפי פי שניים קצב אות השעון שבו הם פועלים, כלומר, קצב נתונים.

בדרך כלל, מצייתים למוסכמה DDRx – yyyy לצורך ציון שבבי הזיכרון. ואולם, שבבי זיכרון אינם זמינים כך סתם. הם מולחמים על מעגלים מודפסים (PCB) זעירים, שנודעים בשם מודולי זיכרון, המהירות שלהם מתוארת בביטוי PCx – zzzz. בביטוי PCx-zzzz ה-x מייצג את דור הטכנולוגיה (שהוזכר לעיל) וה-zzzz מציין את רוחב הפס המרבי, זאת אומרת, קצב העברה מרבי במגה – ביית בשנייה (Mbytes/s).

קצב העברה מרבי – אות שעון x מספר הסיביות/8

מאחר שמודולי זיכרון מעבירים 64 סיביות בפעם אחת, “מספר הסיביות” יהיה 64.

על כן, אפשר לפשט את הנוסחה לביטוי הבא:

קצב העברה תיאורטי מרבי = אות שעון x 8

כמו כן, אפשר לראות את מתח ההפעלה ואת הגודל של המודול, כפי שהם מצוינים על מודול הזיכרון. באיור 2, אפשר בקלות להבחין בין שבבי הזיכרון ומודול הזיכרון. הגופים השחורים הקטנים שמשובצים על המעגל המודפס שצבעו ירוק, הם שבבי הזיכרון, והמעגל המשולב כולו, הוא מודול הזיכרון.

אם כן, מאיור 1 אפשר לקבל את המידע הבא. מודול הזיכרון מורכב משבבי זיכרון שפועלים באות שעון זמן אמת של 800 מגה הרץ – הווה אומר, קצב הנתונים שלו הוא 1600 מגה הרץ, והוא תומך בהעברת נתונים בין הבקר והמודול, בקצב מרבי אפשרי של 12800 מגה ביית בשנייה. יש לו נפח של 8 ג’יגה סיביות.

כעת אם נעבור לפרמטרי התזמון, אנו רואים שהקוד 9-9-9-25 והקוד 9-9-9-24 מופיעים על מודול הזיכרון באיור 1 ובאיור 3, בהתאמה.

מה בדיוק המשמעות של התזמון A-B-C-D (או לפעמים CLA-B-C-D)? לעתים, לא ברור כיצד שני מודולי זיכרון עם אותו קצב העברת נתונים מרבי, שפועלים באותה תדירות אות שעון, מגיעים לביצועים שונים. הסיבה לכך טמונה בעובדה שיש להם פרמטרי תזמון שונים. תזמוני הזיכרון נתונים באמצעות סדרה של מספרים; למשל כפי שנראה באיור 3, “9-9-9-24”.

מספרים אלו הם אמת מידה לזמן שלוקח לשבב הזיכרון לבצע פעולות פנימיות. המספר מציין את כמות מחזורי אות השעון שנדרשים לזיכרון כדי לבצע את הפעולות הפנימיות. ככל שהמספר קטן יותר, כך הזיכרון יהיה מהיר יותר. בהמשך מופיע תיאור של הפעולות המצוינות על ידי המספרים האלו:

CL-tRCD-tRP-tRAS () – על מנת להבין בצורה טובה יותר את הפעולות האלו, ננסה תחילה להבין את תהליך הגישה אל SDRAM.

גישה אל זיכרון

DR SDRAM

הזיכרון מסודר בתבנית דמוית רשת, עם שורות ועמודות. הנתונים המאוחסנים מגיעים בבלוקים ומוגדרים על ידי קואורדינטות של שורה ועמודה. הצעדים ש”עושה” בקר הזיכרון כדי לגשת אל הנתונים בשבב SDRAM, עוקבים בסדר הבא:

ראשית, השבב SDRAM נמצא במצב סרק או במצב שבו הוא מבצע את הפעולה הקודמת. הבקר מפיק את הפקודה “פעיל” (Active). היא מפעילה שורה מסוימת, כפי שמצוין בקווי הכתובת בשבב SDRAM לצורך גישה. פקודה זו בדרך כלל נמשכת כמה מחזורי אות שעון. לאחר ההשהיה, מפיקים את כתובת העמודה ואת הפקודה “קריאה” (Read) או “כתיבה” (Write). בדרך כלל, אפשר לחזור על הפקודה “קריאה” או “כתיבה” מדי מחזור אות שעון עבור כתובות שונות של עמודות (או אפשר לבצע קריאת מצב פרץ – burst). ואולם, נתוני הקריאה אינם זמינים אלא לאחר שיחלפו כמה מחזורי אות שעון, מפני שהזיכרון עובר בצינור עיבוד נתונים (pipeline). כאשר יש דרישה לגישה לשורה אחרת, צריך לבטל את השורה הנוכחית, על ידי כך שמפיקים את הפקודה “טעינה מוקדמת” (precharge). הפקודה לטעינה מוקדמת תשתהה כמה מחזורי אות שעון ספורים, לפני שאפשר יהיה להפיק את הפקודה “פעיל”.

כעת נוכל לחקור את ההגדרה המפורטת של כמה פרמטרי תזמון שונים.

זמן אחזור CAS (): זמן אחזור CAS (זמן אחזור של הבהוב – strobe – גישה לעמודה), נודע גם בשם “זמן גישה”, הוא פרמטר הזיכרון החשוב ביותר, והוא הראשון בסדרת המספרים. זה זמן ההשהיה שבין הרגע שבו בקר זיכרון מודיע למודול הזיכרון לגשת אל עמודת זיכרון מסוימת במודול זיכרון RAM, לבין הרגע שבו נתונים ממיקום מערך נתון הופכים להיות זמינים בפיני המוצא של המודול. בזיכרון מסוג DDR SDRAM נתון זה מוגדר במחזורי אות שעון, לעומת זיכרון DRAM אסינכרוני, שבו נתון זה מוגדר בננו-שניות.

השהית זמן RAS לזמן CAS (): הקיצור tRCD משמעו זמן השהיה בין כתובת השורות לכתובת העמודות. בתוך הזיכרון, תהליך הגישה לנתונים מאוחסנים מושג על ידי ראשית הפעלה של השורה, לאחר מכן, העמודה שבה היא ממוקמת. tRCD הוא הזמן שנדרש בין הרגע שבו בקר הזיכרון מפיק הבהוב (strobe) של כתובת שורה (RAS) לבין הרגע שבו אפשר להפיק את הבהוב כתובת העמודה (CAS) במהלך פקודת קריאה או פקודת כתיבה עוקבות. ככל שהזמן הזה יהיה פחות, כך ייחשב לטוב יותר, מפני שקריאת הנתונים תיעשה מוקדם יותר.

טעינה מוקדמת של RAS (): בכל פעם ששורה חדשה אמורה להיות מופעלת למטרה של גישה לסיבית נתונים, צריך להפיק פקודה שנקראת “טעינה מוקדמת” כדי לסגור את השורה הפעילה כבר. זמן טעינה מוקדמת RAS, tRP הוא המספר של מחזורי אות שעון הנדרשים כדי לסגור את הגישה לשורה פתוחה של זיכרון, ולפתוח גישה לשורה הבאה הנדרשת.

השהיה בין מצב פעיל לטעינה מוקדמת (tRAS): לאחר שהופקה הפקודה “פעיל”, לא ניתן יהיה להפיק פקודת “טעינה מוקדמת” נוספת, אלא לאחר שזמן tRAS חלף. אם כך, tRAS הוא מספר מינימלי של מחזורי אות שעון שנדרשים כדי לגשת אל שורה מסוימת של נתונים בזיכרון, בין בקשת הנתונים (פעילה) לבין הפקודה טעינה מוקדמת. באופן בסיסי הפרמטר הזה מהווה הגבלה לנקודה שבה הזיכרון יכול להתחיל בקריאה (או בכתיבה) של שורה אחרת.

הערה: כל ארבעת הפרמטרים פועלים עם שעון זמן אמת של הזיכרון, כלומר במחצית אות השעון המוגדר. זיכרון עם CL=4 אינו אמור להיות איטי יותר מאשר זיכרון עם CL-3. הכל תלוי באיזו תדירות אות שעון שניהם פועלים, ובהתאם לכך, אפשר לחשב את זמני האחזור המוחלטים של שניהם.

כדי להביו טוב יותר, אפשר לעיין בתרשים התזמון של זיכרון עם פרמטרי תזמון 3-3-3-10 (משוערים) שמופיע באיור 4.

לסיכום המאמר, אנו יכולים לתמצת את פרמטרי התזמונים בדרך הבאה:

זמן אחזור CAS () הוא הזמן שנדרש לקריאה של הסיבית הראשונה מהזיכרון, מתוך זיכרון DRAM כאשר השורה הנכונה כבר פתוחה.

הזמן שנדרש כדי לקרוא את הסיבית הראשונה מתוך זיכרון DRAM מבלי שתהיה שורה פעילה כלשהי, הוא tRCD + CL.

זמן הקריאה של הסיבית הראשונה של הזיכרון מתוך זיכרון DRAM כאשר שורה לא נכונה פתוחה, הוא tRP + tRCD + CL.

המספר של מחזורי אות שעון הנדרשים בין הפקודה “פעיל” לבין הפקת הפקודה “טעינה מוקדמת” הוא tRAS.