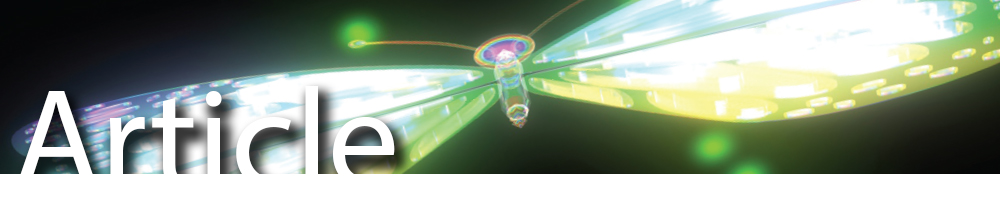

למרות ההתקדמות הניכרת במעגלי מיקרו גל מוכללים מבוססי סיליקון, טכנולוגיות III/V ממשיכות להראות יכולות משופרות המציעות תמורות (trade off) במונחי NF, הגבר, הספק ולינאריות ליישומים שונים. ביניהם תקשורת אל-חוטית (wireless) תשתיות סורקי אבטחה, מכ"ם ומכשור. היסטורית, ה"חולשה" של טכנולוגיותIII/V היתה: האפשרות המוגבלת לתכלל (integration) אותה. במאמר זה נראה כיצד מתאפשר בתהליכי PHEMT D/E לממש פונקציות אנלוגיות כגון מסיטי פאזה

למרות ההתקדמות הניכרת במעגלי מיקרו גל מוכללים מבוססי סיליקון, טכנולוגיות III/V ממשיכות להראות יכולות משופרות המציעות תמורות (trade off) במונחי NF, הגבר, הספק ולינאריות ליישומים שונים. ביניהם תקשורת אל-חוטית (wireless) תשתיות סורקי אבטחה, מכ"ם ומכשור. היסטורית, ה"חולשה" של טכנולוגיותIII/V היתה: האפשרות המוגבלת לתכלל (integration) אותה. במאמר זה נראה כיצד מתאפשר בתהליכי PHEMT D/E לממש פונקציות אנלוגיות כגון מסיטי פאזה

(Phase Shifter) ומנחתים (Attenuators) עם ביצועים עיליים (State of the Art), על אותו שבב, תוך שימוש בפונקציות בקרה ספרתית. לדוגמא: ממירים טוריים למקביליים.

המימוש הוא בשבבי ליבה (Core Chips) הכלולים באנטנות מונהגות אלקטרונית

(steerable Antennas) מ-Ka band to C כיום, ל-E band בעתיד הקרוב.

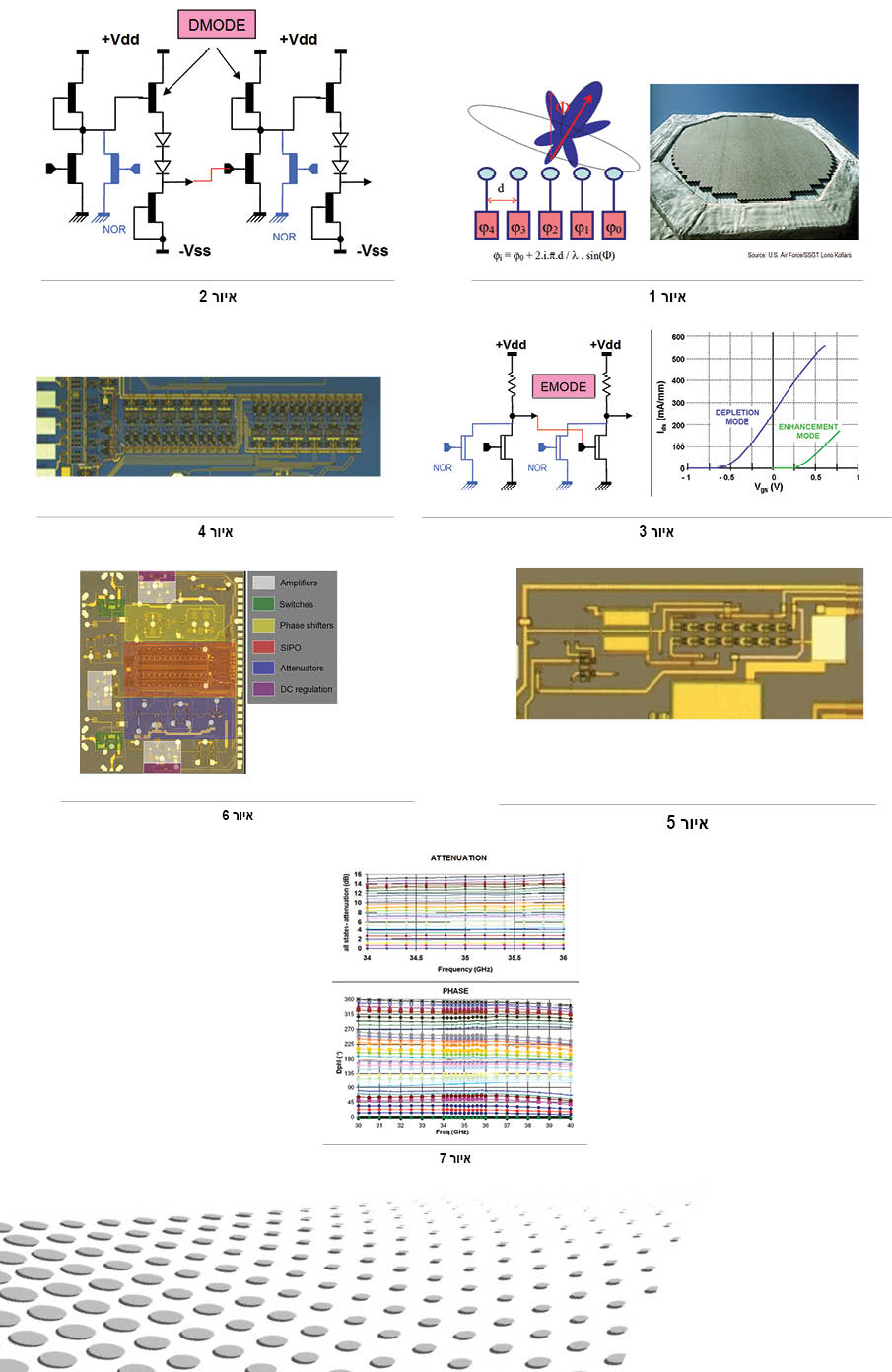

אנטנות אלה אינן "סובלות" מבעיות רעש, אמינות, ותחזוקה כמו המערכות המונהגות מכנית המוכרות. בשיטה המדוברת, הקליטה ו/או השידור מתבצעים בהעברת מטריצה של פרמטרים בלתי תלויים המשודרים לאלמנטים המשדרים ע"מ לייצר את האלומה המוכוונת. האוריינטציה של האלומה מושגת תוך שימוש במסיטי פאזה משתנים

(Variable Phase Shifter) המחוברים לכל אלמנט שידור. (ראה ציור 1 ומשוואה 1 בגוף הציור).

רכיב ליבה (Core Chip) הוא מערכת בקרה שלמה הכוללת מסיטי תדר, מנחתים, מתגים מגברים דלי רעש ומגברי הספק על רכיב יחיד הכולל גם מעגלי בקרה ספרתית. מעגלי מיקרוגלים רבי פונקציות אלה מאתגרים מאד. עליהם להפחית למינימום רעש במוד קליטה Rx, ולהגדיל למקסימום את ההגבר במוד שידור Tx. באותו זמן עליהם לפצות הפסדים במסיטי התדר, מנחתים ומתגים המשתנים בתחום של dB.15 בכך מתמצה היתרון הגדול של טכנולוגיית PHEMT III-V על הסיליקון.

הצורך בשליטה ספרתית על הפונקציות האנלוגיות הללו יוצר גם בעייה ניכרת של התחברות פנימית (interconnection). עבור אנטנה עם אלפי נתיבי קרינה – זה עלול ליצור קושי.

תכלול של בלוק ממיר מוצא ספרתי טורי למקבילי (SIPO), ישירות לרכיב הליבה, הוא יתרון במונחי מחיר/ביצועים. הוא "מתיר" את המבוך (maze) של החיבורים הפנימיים למבוא יחיד של נתונים ספרתיים. שיטה אחת (לדוגמא) של מימוש ממיר טורי למקבילי (SIPO) היא להשתמש בכמה טרנזיסטורי מוד איזורי נדידה, לפונקציות הספק, וכמה לפונקציות בקרה – כמודגם בציור 2.

יחד עם זאת, המורכבות של מבנה ה-SIPO ובפרט אספקת המתחים לטרנזיסטורים יוצרת בעיות גדולות. טרנזיסטורי מוד נדידה מותאמים היטב לביצועי הספק ורעש נמוך, אבל טרנזיסטורי enhancement mode הרבה יותר יעילים למימוש SIPO on chip.

מבנה של block E-mode SIPO, מודגם בציור 3. שלא כמו בטרנזיסטורי מוד D, טרנזיסטורי מוד E נקטמים (pinched off) ב-VOLT 0 ומפיקים זרם בעוד מתח השער (gate voltage) הוא חיובי.

יתרון אחד של זה נקרא צימוד ישיר

(direct coupling) באשר מתח השער של הדרגה השנייה יכול להיות מוזן ממקור המתח של DRAIN הדרגה הראשונה.

יתרון נוסף הוא צריכה נמוכה עקב ממתח ברך (knee voltage) נמוך של טרנזיסטורי E- MODE.

אחד התהליכים המתאימים הוא OMMIC ED02AH. התהליך מורכב מטרנזיסטורי D and E- MODE עם 60GHz Ft. העושה אותו מועמד טוב כרכיב יחיד לשילוב במעגלים ספרתיים כגון SIPO ,LNA ,Medium PA, ומתגים on chip. ציור 4 מראה SIPO של 14 סיביות המשתמש ב-600 טרנזיסטורי מוד

E ( טרנזיסטורים לסיבית).

לאנטנה המורכבת ממאות או אלפים של אלמנטים, צריכת זרם DC לכל רכיב ליבה הוא חיסרון. רגולציה DC על הרכיב (ציור 5) תוך שימוש בתהליך E/D GaAs PHEMT מקטין את סה"כ mmW/bit והשפעות סטייה בתהליך, מקטין אל שולי התכנון בקצוות (layout corners) ומפחית את סיבוך המערכת, שכן אין צורך בכיוונון.

דוגמאות מ"העולם האמיתי" מודגשות להלן.

רכיב הליבה הראשון של GHZ

[.Roberto Giordani et al], משלב מסיט פאזה של 6 סיביות (rms error) , מנחת ספרתי של 6 סיביות (0.25dB rms error)

6 מתגים, SIPO של 12 סיביות ומגברים מווסתים (regulated) המפיק במוצא

20dBm. השבב כולו מוצג בציור 6 בקווים מרוסקים ע"מ להדגיש כל פונקציה.

הדוגמא השנייה מדגימה מוצר אזרחי המיוצר בכמות גבוהה שהיא אינטרנט ברוחב פס גבוה ללוויין על גג מכוניות ומטוסים. זהו יישום של Phased Array Antenna

().

אנטנה בודדת מכילה 150 רכיבי ליבה.

כל רכיב משלב מסיט פאזה של 4 סיביות המחובר ל-LNA ו-/SIPO.

הדוגמא השלישית ממחישה את היכולת לתכנן ולהשתמש ברכיבי ליבה בתהליכי E/D עד לפס (Ka band 32-34GHz) וב-2/Ft של התהליך. ציור 7 מדגים את בקרת הניחות של הפאזה של הרכיב בתחום 31-34 GHz.

שים לב לשטיחות (flatness) של הרכיב בתחום זה. תכונה זו היא הכרחית באנטנות המונהגות אלקטרונית. אם הפאזה אינה קבועה לכל רוחב הפס, אז האלומה המצביעה (pointing beam) לאותו כיוון בתדירויות שונות, תידרוש שינוי דינמי של הפאזה לכל אלמנט משדר כתלות בתדר.

כדי להשיג דיוק הצבעה (pointing) במערכת רחבת סרט, שימוש בפונקציית (True Time Delay) הוא הפיתרון [Van Vilet and al]. פיגור קבוע בזמן בתחום רחב, אפשרי אם משתמשים באורכים שונים של קווי מתגים – משום ששינוי הפאזה פרופורציוני לתדר.

לדוגמא, TTD של 5 סיביות הוא בעל 5 אורכים שונים של קווים המאפשרים 64 אפשרויות של זמני השהיה שונים.

עם זאת נציין שתהליך. III/V מגביל את את תחום התדרים שרכיבי הליבה יפעלו בהם. כדי לפתח רכיבי ליבה הכוללים בקרת SIPO על הרכיב, שיעבדו ב-60GHz,

וב-nm100, תהליך true E-mode המנצל את השכבה המטמורפית, יהיה זמין בשנה הבאה

[MEHAR and al].

הוא מציע GHz Ft 300 GHz Fmaxt . תהליך E01MH זה מבטיח מספיק הספק RF וביצועים תוך שימוש בלבדי בטרנזיסטורי מוד E. ההגבר המירבי היציב של דרגה אחת ב-30GHz, הוא dB . זה מוכיח שהגבר מוד E אינו בעייתי כלל.תחום השינוי (swing) של מתח השער הור 0.62, וסף המתח של

100 תומך באינטרציה של מתגים.

תהליכי E/D III/V מאפשרים שילוב של מגברים בעלי ביצועים גבוהים, מסיטי פאזה, ומנחתים הכוללים ממירי טורי למקבילי – בתוך רכיבי ליבה.

רמת השילוב הופכת את המימוש של אנטנות נהוגות פאזה לאפשריות בהוצאה וממדים מינימליים מ-C עד Ka band כיום ואפילו ל-E band בעתיד הקרוב.

מאת: F.ROBERT, R.LEBLANC, J.MORON, A. GASMI, N.SANTOS, M.ROCCHI.