מערכת המכ”ם הייתה משתמשת בעיצוב אלומות היברידי אנלוגי ודיגיטלי. תת-מערכים של מסיטי-מופע במישור האנלוגי עוברים לדיגיטליים במוצאי התת-מערכים לשם עיבוד-המשך של עיצוב אלומה דיגיטלי. מערכת כזו סובלת מרוחב-פס מוגבל והיא לא יכולה לעצב בו-זמנית יותר מאשר אלומה אחת. עיצוב השהיית-זמן דיגיטלית מציע הרבה יתרונות כגון צורת-גל של פולסים בעלת רוחב-פס גדול ואלומות בו-זמניות בזוויות, צורות-גל ותדרים שונים. יכולות אלו נחשבו ליקרות מידי בעבר, אך כיום הן

בעלות-השגה בשל הצפיפות הגבוהה של מכפילים ב-FPGA והשקת

מבוססי-מקמ”ש. מאמר זה יציג את התכנון והמימוש של מסנן בעל השהייה פרקציונלית (fractional delay – FD) המשמשת בסוגיות של עיצוב אלומות כגון רוחב-פס רחב, עיצוב אלומה מסתגל וחיבורים הדדיים בעלי צפיפות גבוהה. ארכיטקטורות עבור מערכי מופע ייחקרו גם כן.

מבוא

עיצוב אלומה דורש אנטנות מרובות הפועלות ביחד כדי ליצור הפרעות בונות והורסות בין אנטנות היוצרות תבנית אלומה ספציפית. על-ידי השהיית האותות המזינים את האנטנות של המערך (על-פי המרחקים ממרכז המופע), ניתן לכוון בהתאם את הכיוון של חזית הגל. ניתן גם להוסיף משקלים על האנטנות בהתאמה כדי למזער את ההספק מכיוונים בלתי-רצויים.

לגבי אותות צרי-סרט, להסטת המופע של אות יש אותה ההשפעה של השהיית האות. מסיטי מופע עבור יישומים רחבי-פס גורמים לפיזור האות – מרכיבי תדר שונים של האות עוברים זמני השהייה שונים. מאידך, שבב השהיית הזמן האמיתי יכול להשהות את האות בפרקי זמן דיסקרטיים, אך סובל מרזולוציה מוגבלת. מסיטי המופע כמו גם השהיית הזמן האמיתית מבצעים עיצוב אלומות במישור האנלוגי בתדר RF. שיקולים נוספים לגבי עיצוב האלומה האנלוגי כוללים את הפסד השילוב מנתיבי האות וכן את העובדה שניתן לעצב אלומה אחת בלבד בו-זמנית אלא אם האנטנות הן מחויצות.

שיטת ה-Fast Fourier Transform הייתה נפוצה מאוד בעיצוב אלומות דיגיטלי בשל המימוש היעיל ביותר שלה. היא פועלת היטב עבור פס צר, אך היא רחוקה מאידיאלית עבור אותות רחבי-פס.

עיצוב אלומה דיגיטלי בהשהיית זמן מלאה מבטל חסרונות של עיצוב האלומה האנלוגי ומספק יתרונות נוספים כגון אלומות בו-זמניות בזוויות, צורות גל ותדרים שונים. ניתן להשיג גם קיטוע שרירותי של מערך ומתן צורה שרירותית של תבנית האנטנה. תכונות אלה הן קריטיות עבור משימות רגישות לזמן (מרובות). עבור אותות רחבי-פס, השהיות זמן עם עיבוד אותות דיגיטלי יכולות לספק תוצאות מדויקות מאוד. יכולות אלו נחשבו ליקרות מידי בעבר אך הן כעת ניתנות להשגה בשל הצפיפות הגדולה של מכפילים ב-FPGA והממשקים הטוריים המהירים הרובוטיים של ADC/DAC.

פרק II מתאר את התכנון והמימוש של מסנן (fractional delay). פרק III מתאר אתגרים אחרים כגון המימוש של רוחב-הפס הרחב, מתודולוגיית התכנון ועיצוב האלומה האדפטיבי. פרק IV דן בארכיטקטורת החיבורים ההדדיים של מערכי מופע בעלי צפיפות גבוהה.

II. מסנן השהייה פרקציונלי

רקע

סימוכין [1] ניתח לעומק את התיאוריה והפתרונות של תכנון מסנני השהייה פרקציונליים. הוא קבע את העובדה שלמסנן השהייה פרקציונלי אידיאלי (המשהה D דגימות) יש היענות לפולסים:

1.

כאשר D הוא ההשהיה הרצויה של רצפי המוצא ו-D יכול להיות פרקציונלי. דבר זה מראה שקונבולוציה עם מסנן אידיאלי מוסט מופע תיצור מוצר מושהה בהתאמה. תכונה זו ניתן להכליל לכל מסנן.

לעיצוב אלומות של מכ”ם יש גם דרישה שיש להפיק זווית חדשה, כלומר השהייה חדשה ומסנן חדש בזמן אמת במהירות ובדיוק רב. שתי החלופות הנפוצות עבור מסנני FD הן Lagrange Interpolation ומבנה Farrow. לא מתאימה ביישום שלנו מאחר שפס המעבר שטוח רק על-יד ה-DC. יש לדגום-על כ-4 פעמים לפני שיהיה לנו פס מעבר די רחב ושטוח. דבר זה יתאים יותר עבור יישום העוקבים אחר המסנן עם המרת-על.

מבנה Farrow מבוסס מסנן המשתמש בקירוב פולינומי נבחר עבור מימוש זה בגין בקרת הספקטרום המדויקת שלו, יחס אות לרעש SNR וגודל ההשהיה. מבנה Farrow הוא גם פשוט למימוש.

פילטר בסיסי

לאות מכ”מי בפס-בסיס יש רוחב פס מסוים והוא בד”כ קוהרנטי ודורש אות מרוכב. קצב הדגימה יכול להיות 25% עד 50% גבוה יותר מאשר רוחב הפס. דרישות אלה מהוות את המפרט הבסיסי לתכנון המסנן. לדוגמה, רוחב הפס של האות הוא 200 מגה-הרץ, או מגה-הרץ מעל DC, קצב הדגימה המזערי יהיה 200 מגה-הרץ. ב-50% דגימת-יתר, קצב הדגימה הוא 300 מגה-הרץ. ברור שאנחנו זקוקים לסוג של מסנן בעל פס מעבר מכוון ל-100 מגה-הרץ.

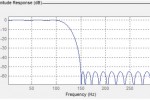

ניתן להסתפק במסנן מעביר-נמוכים רגיל בעל פס חסימה מכוון ל-150 מגה-הרץ או לתדר Nyquist, כמו באיור 1a. מסנן מעביר-נמוכים אכן יתפקד, אך הוא רחוק ממיוטב, מאחר שהוא לא משתמש במלואו ברוחב פס המעבר. למסנן מיוטב יהיה פס מעבר של 100 מגה-הרץ, פס חסימה של 200 מגה-הרץ וקצב דגימה של 300 מגה-הרץ, כמו באיור 1b. מאחר שרוחב פס המעבר מכפיל את זה של המסנן הראשון, המסנן השני ייקח רק מחצית מהסנף (tap) של הראשון.

שים לב שתדר הקיטעון של המסנן השני יהיה בתדר Nyquist או 150 מגה-הרץ. זהו מסנן Nyquist המוגדר על-ידי

2.

כאשר L=2, הוא מסנן מחצית הפס. כאשר L=1, H הוא מסנן Nyquist (פס מלא) מושלם עבור דגימה מחדש.

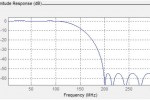

נא לשים לב ש-Matlab איננו מפיק מסננים כאלה כגון פס החסימה שעובר את תדר ה-Nyquist. איורים 2a ו-2b מראים מסננים כאלה בכחול. זה לא שימושי מאוד בעצמו. היענות התדר היא 1 עבור כל תדר. להיענות הפולסים יש אחד באמצע וכל שאר המקדמים הם אפסים. דבר זה מכונה מסנן FIR מעביר-הכל ב-[1] – ברור בשל תכונתו של מעביר-הכל.

אנחנו מתעניינים בצורת השירבוב (interpolation) או דגימת-היתר. איורים 2a ו-2b מראים את הגרסה המשורבבת באדום. תדר הקיטעון של הגרסה המשורבבת הופך למסנן מעביר נמוכים ויש לו תדרי קיטעון ב- מנורמל. זכור שהענות הפולס של מסנן מלבני בעל רוחב-פס B וזמן t היא

3.

המשוואה (2) מראה שאם היענות הפולס שמרה על אותה הצורה, לפונקציית ה-sinc המשורבבת או בעלת דגימת-יתר 4x היה רוחב-פס 1/4 מנורמל. דבר זה מסביר מדוע היענות התדר של המסנן המשורבב 4x (אדום באיורים 2a ו-2b) מתכווצת ל-25% של הלא-משורבבת. תדר הקיטעון הוא באמת ב- התדרים המנורמלים. דבר זה אומר שאם אנחנו לא יכולים לתכנן מסנן Nyquist ישירות, אנחנו יכולים לתכנן גרסה בעלת דגימת-יתר – שזה בדיוק מה שאנחנו צריכים.

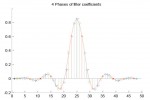

ניתן לראות את מקדמי המסנן בעל דגימת-יתר 4x כ-4 מופעים של מקדמי המסנן FD המשולבים ביחד כמו באיור 3. ניתן לשרבב כל השהייה הנופלת ביניהם מהמופעים המחושבים מראש. ככל שיש לנו יותר מופעים, כך יהיה המסנן המוצג מדויק יותר.

קירוב פולינומי

המשוואה (4) מסופקת על-ידי [2] כדי להעריך את כמות דגימת-היתר של המקדמים, N, עבור רוחב נתונים נתון של b ביטים, כאשר משתמשים בשרבוב ליניארי בין שני שכנים.

4.

טבלה 1, המבוססת על (4), מראה את הקשר בין רוחב האות המקובל והמספר המזערי של דגימות-יתר כדי לשמור על אותה הנאמנות. לכן, דגימת-יתר של 64x תספק מספיק נאמנות עבור אות של 14 ביט, או כ-84dB SNR.

דבר זה הוא שונה במקצת מהמושג המקורי של מבנה Farrow המציינת שפולינום יחיד משמש עבור כל סנף של השהייה פרקציונלית של המסנן. כאן, בינומים בעלי סדר נמוך רבים משמשים עבור סנף מסנן יחיד. בתלות בהשהייה, נבחר את הבינום התואם.

מימוש

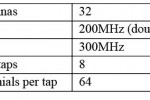

אם כי המימוש שלנו מאפשר מספר הניתן לעיצוב של אנטנות, רוחב-פס, קצב דגימה, מספר הסנפים של המסנן ויחס דגימת-היתר שלו, דרישות התכנון בטבלה 2 משמשות לשם הדגמה.

כדי לספק 8×64 או 512 בינומים, דרושים 513 מקדמי דגימת-יתר או סדר גודל של 512 מסננים. כל בינום מיוצג על-ידי שני מקדמים סמוכים. הבינום הראשון מיוצג על-ידי המקדמים 1 ו-2, והבינום השני מיוצג על-ידי המקדמים 2 ו-3, וכך הלאה. סנף המסנן הראשון מכוסה על-ידי הבינומים 1 עד 64 המכוסים בתורם על-ידי המקדמים 1 עד 65. הסנף השני מכוסה על-ידי הבינומים 65 עד 128 המכוסים בתורם על-ידי המקדמים 65 עד 129.

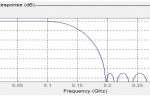

מאפייני המסנן ייראו כמו האיור 1b. איור 4a מראה את קביעת הפרמטרים של תכנון מסנן כזה תוך שימוש בכלי התכנון של (FDATOOL). כדי ליצור מסנן בעל דגימת-יתר, תדר הדגימה Fs וסדר המסנן מוכפלים ראשית בגורם דגימת-היתר, 64 במקרה זה. שנית, וודא שמאפיין פס החסימה עונה לדרישות. אם לאו, כוון את ניחות סדר המסנן בהתאם. שיפוע פס החסימה מוגדר כך שתמונות ספקטראליות נדחות או חופפות לא ייבנו.

איור 5 מראה את המימוש ההתנהגותי של יצירת מקדמי השהייה פרקציונליים ב-Simulink עם כלי התכנון (Digital Signal Processing Builder Advanced) של Altera. ההשהיה הרצויה ניתנת לפירוק למנה שלימה ופרקציונלית של מחזור הדגימה. השהיית השלם מושגת על-ידי השהייה דרך (First In First Out) ואינה מוצגת כאן. ה-FD הופך ל-PhaseAddr ו-FractionalPhaseAddr. לדוגמה, אם FD הוא 0.2, או 12.8/64 (עבור 64 בינומים לסנק), ה-PhaseAddr הוא לכן 12

וה-FractionalPhaseAddr הוא 0.8.

מקדמי דגימת-היתר מאוכסנים בזיכרון או ROM (Read Only Memory) – SRC_CoefRom באיור. לכל זיכרון יש שתי פיתחות קריאה; אחת בשם PhaseAddr והשניה ב-PhaseAddr plus one. לכן, שני מקדמי הבינומים זמינים באותו הזמן. המקדם FD הסופי (של הסנק המתאים) משורבב ביניהם. ה-“(32)” בסוף סוג הנתונים פירושו שהאות הוא וקטור בעל 32 מרכיבים המתאימים ל-32 אנטנות. גודל הווקטור וסוג הנתונים מועברים אוטומטית על-פני נתיב הנתונים. איור 6 (המתאים ל-SRC_scope2 באיור 5) מראה ש-8 מקדמי ה-FD מחושבים ומועברים ל-FIR לפי הסדר, אך עם כל 32 האנטנות מחושבות במקביל.

איור 7 מראה את תהליך הקונבולוציה דרך מערך של מסננים. ה-“Array of FIRs” הוא מרכיב בעל רמה גבוהה מיצדי (parameterized) כדי ליצור 32 FIR עצמאיים במקביל, כל אחד עם פיתחת מבוא מרוכבת ופיתחת עדכון מקדמים. התקפות של האות מסומנת על-ידי פיתחות “v” במבוא ובמוצא. גוש הסקאלה רק מנחית את מוצא ה-FIR מ-35 ביט ל-14 ביט.

אם כי איורים 5 ו-7 מראים את המימוש ההתנהגותי ברמה גבוהה, ניתן לסנתז את התכנון ישירות אל החומרה על-ידי הכלי DSPBA. הכמות הנכונה של אוגרי החפיפה אשר תוכנס אוטומטית בשעת החישוב תלויה במהירות שעון ההפעלה, סוג ההתקן, גודל הווקטור או הפס, מספר היציאות והמעגל.

ארכיטקטורה זו יעילה מאחר שניתן לחשב מראש שלבים רבים של מסנן ה-FD. מקדמי ה-FD בזמן אמת דורשים רק שרבוב פשוט. מימוש של ארכיטקטורה כזו הוא יעיל עבור FPGA מאחר שכגוש FPGA.

() מופיע בגודל 9Mbits או 20Mbits (תלוי במשפחת ה-FPGA), וניתן לעיצוב בצורה של 512×18 bits או 1024×20 bits. אם כי ישנם 513 מקדמים סימטריים, כלי הסנתוז מספיק חכם כדי לזהות שהמקדם 1 ו-513 הם זהים (מאחר שמסנן דגימת היתר הוא סימטרי) ולקצץ אותם ל-modulo 512. כל אנטנה דורשת לכן גוש RAM אחד ומכפיל אחד לשם הפקת המקדמים.

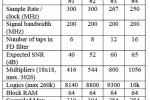

הקונבולוציה הממשית עם אות מרוכב דורשת 2 מכפילים לכל סנף של מסנן. עבור מסנן בעל 8 סנפים ו-32 אנטנות, דרושים 512 מכפילים לכל אלומה. לכן חשוב כל כך להשתמש במסנן מיוטב או כמעט מיוטב. טבלה 3 מראה את שימושי המשאב עבור 32 אנטנות לאלומה עבור מפרטים שונים. השימושים כוללים גם לוגיקות אחרות כגון המרה של זווית האלומה להשהיות נתיב בודדות. ל-FPGA גדול איכותי ב-28nm יש כ-4000 מכפילים. ניתן לממש כ-4 עד 8 אלומות בו-זמניות ב-FPGA אחד, תלוי במפרטים.

דיוק האלומה תלוי בדיוק ההשהיה של האנטנות הבודדות, התלוי בעצמו בחישוב המופע. המופע מחושב לפי כתובת של 16-ביט ומחזור דגימה של 3.3 ננו-שניות. דבר זה נותן לנו רזולוציה גבוהה מ-0.1ps או מרחק תנועת האות של 0.03 ממ’. בהנחה שמרווח האנטנות הוא 0.5 lambda וה-lambda הוא 1 מ’, הרזולוציה הזוויתית היא טובה מ-0.005 מעלה. סביר ביותר שצוואר הבקבוק עבור הדיוק הזוויתי יוגבל על-ידי גורמים אחרים שלא מוזכרים כאן.

אתגרי מימוש אחרים

A. תכנון ברמת המערכת

בניית תכנוני DSP ב-HDL או FPGA דורשת לרוב שתי קבוצות של מהנדסים – מהנדסי מערכת וחומרה. מהנדסי המערכת מממשים את האלגוריתמים ב-Matlab או C ומהנדסי החומרה נוטלים את המפרטים ובונים חומרה המתאימה לדגם של Matlab או C. Simulink מנסה לגשר על הפער עם תכנון מבוסס דגם ומשווקי ה-FPGA מספקים מערכי גוש הניתנים לסנתוז כך שמהנדסי המערכת יוכלו לתרגם את התכנון לחומרה. מכשול גדול של מתודולוגיה זו היא בכך שהמהנדסים צריכים לעבד את התכנונים ידנית. FPGA איננו פועל כה מהר כמו ASIC ועיבוד האוגר הוא הטכניקה לסנכרן את התכנון לעתים קרובות יותר כך שניתן יהיה להשיג מהירויות הפעלה גבוהות יותר. זה עשוי להיות תהליך מייגע.

הכלי DSPBA של Altera פתר את הבעיה על-ידי שילוב עיבוד אוטומטי המבוסס על סוג ההתקן, מספר היציאות, מהירות ההפעלה, גודל האפיק והתכנון. המתכנן יכול להתמקד יותר בפיתוח ומימוש האלגוריתם. ההעברה האוטומטית של גודל הווקטור וסוגי הנתונים פירושה שתכנון מבוסס DSPBA ניתן לעיצוב ראשוני בשעת החישוב – צריך רק להכניס את גודל הווקטור וסוג הנתונים במבוא. הכלי תומך גם בנקודות קבועות וגם בנקודות צפות.

איור 8 מראה את הרכיבים העיקריים של תכנון עיצוב אלומה זה עבור מכ”ם פולסים ב-DSPBA. הוא מתחיל ביצירת צורת גל (ציוץ), עיצוב צורה בשידור, הדמיה של הפסד מרחב חופשי, הד מטרה ורעש מקלט, עיצוב אלומה בקליטה, צמצום הפתח ולבסוף דחיסת הפולס. השרשרת המלאה נבנתה כך שניתן לבדוק ולבחון אותה בכרטיס פיתוח FPGA. נא רשום שהשידור והקליטה מחלקים את אותו מנגנון עיצוב האלומה בהשהיית זמן מאחר שמכ”ם פולסים אינו משדר וקולט באותו הזמן.

החומרה מבוקרת על-ידי תסריט Matlab דרך API ו-USB . ה-USB הוא המוליך של אפיק מערכת (המכונה קונסולת המערכת) שהוא חלק אינטגראלי של כלי Altera עבור ניפוי ובדיקה.

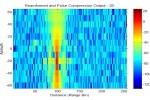

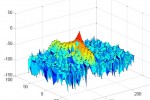

התסריט מעצב את החומרה בזמן אמת עם רוחב-פס ואורך של צורת הגל של הפולס, זווית שידור עיצוב האלומה, מיקום המטרה וזווית קליטת עיצוב האלומה, ועוד. התסריט של Matlab יכול גם לקרוא את התוצאה לשם ניתוח. איור 9a ו-9b מראה את התוצאות שנלכדו בחומרה ונותחו ב-Matlab. אלומת הקליטה מעוצבת לסרוק בין -60 ל-60 מעלות ברזולוציה של 2 מעלות ולמצוא את המטרה ב–20 מעלות ו-bin 100. התכנון המלא ואימות החומרה הושלמו ב-4 חודשים עם DSPBA. זמן הפיתוח היה לפחות כפול בגישה של תכנוני מערכת ו- HDL נפרדים.

B. שיקול רוחב-הפס

כפי שצוין, דוגמת עיצוב האלומה נבנתה עם רוחב-פס אות של 200 מגה-הרץ ומהירות שעון FPGA של 300 מגה-הרץ. מה אם דרישת רוחב-הפס של האות נהיית 400 או 600 מגה-הרץ? אותו ה-FPGA אינו יכול לפעול ב-600 או 900 מגה-הרץ. כלי ה-DSPBA התכונן עבור נסיבות כאלה שקצב הדגימה גבוה מקצב השעון וסיווג אותו כ-Super-Sample Rate (). רכיבים איכותיים עיקריים של DSPBA כגון (Numerical Controlled Oscillator), מסננים ו- (Fast Fourier Transform) תומכים ב-SSR. לגבי המסננים, הכלי בודק את קצב הדגימה וקצב השעון, ואם קצב הדגימה הוא מכפלה שלמה של קצב השעון, מיוצרים שלבים מקבילים מרובים. מהצד השני, אם קצב השעון הוא מכפלה שלמה של קצב הדגימה, התכנון מקופל והמכפילים משמשים מחדש.

C. עיצוב אלומה מסתגל

עיצוב אלומה בהשהיית זמן לבדו אינו מספיק עבור דרישות המכ”ם של היום. מכ”ם חדיש צריך להיות מסוגל לטפל בחסימה. עיצוב אלומה מסתגל מביא בחשבון את ההשפעה של אות חוסם ומנסה לבטל את ההפרעה. השיטה הנפוצה ביותר היא (Sample Matrix Inversion) והיא מבוססת על העיקרון של סינון התאמה (match filtering). כדי לבצע זאת, ההפרעה (לבדה) מודגמת או מאוחזרת מקוביית נתוני המכ”ם, והמקדם המסתגל h ניתן למצוא על-ידי

4.

כאשר S היא מטריצת ההפרעה, t הוא וקטור ההנחיה או כיוון ההסתכלות, ו-k הוא קבוע הנרמול.

כדי למצוא את h, יש להפוך את S וזה מבוצע לרוב על-ידי פירוק Cholesky או QR. שניהם דורשים נקודה צפה לשם ייצוב (בשל יכולתו לטפל במספרים קטנים). פירוק Cholesky הפועל במטריצת שונות משותפת (covariance) צריך גם תחום דינמי רחב שהנקודה הצפה מציעה. נקודה צפה Single Precision מציעה מנטיסה של -24ביט (כולל את ה”l” המובן מאליו) ומעריך בעל -8ביט, ויש לו מספיק דיוק ותחום דינמי כדי לשמור על שגיאה מצטברת נמוכה. שני הפירוקים Cholesky ו-QR נבנו עם הנקודה הצפה של Altera DSPBA, וניתנים לשילוב עם תכנון עיצוב האלומה בעתיד. פירוק Cholesky הוא פשוט יותר ומשיג תפוקת פירוק גבוהה יותר. טבלה 4 מראה את הביצועים של פירוק Cholesky עם גודל מטריצה וגודל וקטור שונה. גודל הווקטור מתייחס למספר יחידות העיבוד במקביל. מספר הערוצים מתייחס למספר המטריצות המפורקות בצורת סירוג (interleaving) בזמן.

GPU ו-GP-GPU (General Purpose – Graphic Processing Unit) שימשו בעיבור מכ”ם back end כגון עיצוב אלומה מסתגל ו-STAP (Space Time Adaptive Processing) חלקית בשל יכולת הנקודה הצפה שלו. אולם, GPUs צורכים הרבה יותר הספק מאשר FPGA. המכפילים הפיזיים ב-FPGA כיום הם עדיין בנקודה קבועה, אך הם משמשים למימוש נקודה צפה. דבר זה היה מאוד לא יעיל אם כל עיבוד בנקודה צפה היה מומר ראשית לנקודה קבועה (אי-נרמול), מעובד ומומר בחזרה לנקודה צפה (נרמול), כמו בפעולות של GPU. בשל הזמינות של מכפילי 27×27 ו-36×36 והמוֹתרות של ניתוח כל שרשרת העיבוד בזמן החישוב, כלי ה-DSPBA מחפש הזדמנויות בהן השימוש ברוחבי מנטיסה גדולים יותר יכול להקטין את הצורך בנרמול ואי-נרמול. כאשר דרוש, הנרמול והאי-נרמול יכולים להיות ממומשים ביעילות על-ידי מכפילים במקום מסיט חבית רחב הבנוי מלוגיקה פרימיטיבית.

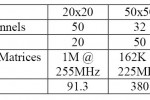

חיבור הדדי

בעיה אחת שהתת-מערך מטפל היא להקטין את מורכבות החיבורים ההדדיים בין אנטנות ויחידות עיבוד האות על-ידי חיבור של אנטנות מרובות בתוך תת-מערך אחד. אולם, כדי למרב את יתרונות עיצוב האלומה, לכל אנטנה צריך שיהיה ה-ADC/DAC משלה. ל-ADC/DAC ממשק מקבילי ולכן הוא מגביל את מספר ה-ADCs/DACs המתחברים ל-FPGA אחד. JESD204B, תקן ממשק טורי עבור ממירי נתונים שנקבע ביולי 2011, מאפשר רוחב-פס גס של עד 12.5Gbps או עומס של עד 10Gbps תוך שימוש בזוג יחיד של אות הפרשי. זמין כעת ADC של -16ביט ב-250Msps עם ממשק של 6.25Gbps. חיבור JESD204B מאפשר התקנים מרובים ונתיבים מרובים. התקן גם מספק אמצעי סנכרון לאורך החיבור. אם כי החלפת ממיר-מופע בזוג של ADC ו-DAC עשויה להיות יקרה יותר כעת, פער המחיר עתיד לקטון בעתיד. הריבוי של שוקי אלחוט גם גורם להעלאת הביצועים ומנמיך את העלות של התקנים כאלה. טבלה 5 מציגה את המספר המרבי של מקמ”שים ומכפילים ב-FPGA 28nm ו-nm20 של Altera. כל המקמ”שים ב-FPGAs אלה יכולים לעמוד בהרבה יותר מהקצב של 12.5Gbps.

עם הממשק הטורי, כל ADC או DAC דורש רק 2 פינים וניתוב ניהול התעבורה הוא לכן הרבה יותר פשוט. הטכנולוגיה של כרטיסי מעגלים מודפסים יכולה לבקר את העכבה עד כדי כדי להקטין את הפסדי השילוב וההעברה. אורך העקבה יכול בנקל לעלות על 50 סמ’. יישומי עיצוב האלומה דורשים שהשהיות עקבה מה-ADCs/DACs אל ה-FPGA יתאימו היטב. במקום, ניתן לקזז אותם בחישובי זמן ההשהיה על-ידי הוספת גורם (קיזוז עקבה) עבור כל אנטנה. בדרך זו ניתן לכייל בזמן אמת את מערכת האנטנה בשלמותה.

כדי לטפל במאות או באלפי אנטנות, אפשר להשתמש בגישה הירארכית של שתיים או יותר שכבות FPGA כדי לחלק את האותות ולצבור אותות קליטה. איור 10 מראה דוגמה של 1024 אנטנות דרך 2 שכבות של FPGA המתארות את כיוון הקליטה. נתיב השידור זהה, אך בכיוון הפוך. השכבה הראשונה (עליונה) פועלת כשכבה של תת-מערכים (דיגיטליים) ולכל תת-מערך יש 32 מבואות אנטנה ו-N מוצאים. כל מוצא הוא סכום חלקי של זווית עיצוב אלומה מסוימת. השכבה השנייה משלבת את הסכומים החלקיים ומייצרת את המוצאים של האלומה הסופית. לכן, לוגיקה של מסנן FD דרושה רק בשכבה הראשונה, ומספר האלומות הבו-זמניות, K, יהיה מוגבל על-ידי מספר המכפילים ב-FPGA. ברור ש-N צריך להיות פחות או שווה ל-K. אלומה צריכה רק לדרוש תת-מערך של אנטנות ושה-1024 אנטנות יהיו מופרדות ב-M חלקים. המספר המרבי של אלומות בו-זמניות יהיה אם כן M*N.

סיכום

תכנון ומימוש מעשי של מסנן FD מיוטב בהקשר לעיצוב אלומה בהשהיית זמן תואר במאמר. סוגיות קשורות כגון מתודולוגיית תכנון, גמישות רוחב-הפס, דרישת הנקודה הצפה עבור עיבוד פסי הנתונים של המכ”ם נחקרו גם כן. השימוש בכלי התכנון הנכון הוא מכריע עבור תכנוני עיבוד נתונים מורכבים וזמן מחזור תכנון קצר. ה-DSPBA של Altera תוכנן כדי לדון באתגרים אלה ויוסיף להתפתח בכיוון זה. לבסוף, ארכיטקטורת החיבורים ההדדיים עבור מערך מופע צפוף נחקרה. כל הטכנולוגיות והרכיבים הדרושים עבור עיבוד אלומה בהשהיית זמן הם זמינים כיום והם עשויים לשנות את התפתחות תכנוני המכ”ם.

סימוכין

T.I. Laakso, V. Valimaki, M. Karjalainen, U.K. Laine, “Splitting the

[1] unit delay: Tools for fractional delay filter design”, in IEEE Signal

Processing Magazine (1996) 30-60

[2] F. J. Harris, Multirate signal processing for communication systems,

Upper Saddle River, NJ; Prentice Hall, 2004.

[3] M. A. richards, J.A. scheer, and W. A. Holm, Principles of Modern

Radar: Basic Principles, Raleigh, NC: SciTech Publishing, May, 2010

[4] C.W. Farrow, “A continuously variable digital delay element”, in

Proceedings of International Symposium on Circuits and Systems, vol.

3, 1988, pp. 2641-2645,.

[5] M. Parker, “Radar Processing: FPGAs or GPUs?”, San Jose, CA: Altera

Corporation, May, 2013

[6] S. Demirsoy, and M. Langhammer, “Fused datapath floating point

implementation of Cholesky decomposition”, High Wycombe, UK:

Altera Corporation, 2009

[7] DSP Builder Handbook, Vol3: DSP Builder Advanced Blockset”, San”

Jose, CA: Altera, May 2013

[8] “ Flow An Independent Analysis of Altera’s FPGA Floating-point DSP Design

Berkeley, CA. Berkeley Design Technology, Inc. 2011

הכתבה נמסרה באדיבות חברת איסטרוניקס

- איור 1a. מסנן מעביר-נמוכים עם Fpass/Fstop/Fs=100/150/300 Mhz

- איור 1b. מסנן Nyquist עם Fpass/Fstop/Fs=100/200/300 Mhz

- איור 2a, 2b. מסנן Nyquist והגרסה המשורבבת 4x שלו

- איור 3. 4 מופעים של מקדמי מסנן

- איור 4a: תכנון מסנן בעל דגימת-יתר

- איור 4b: מאפייני פס החסימה של מסנן Nyquist בעל דגימת-יתר

- איור 5. סכימה המציגה את ייצור מקדמי ה-Fractional Delay

- איור 6. עדכון מקדמי ה-FD

- איור 7. סינון והתאמה של FD

- איור 8. תכנון ברמה גבוהה של עיצוב האלומה של מכ”ם פולסים

- איור 9a. מוצא עיצוב האלומה בהשהיית זמן (מראה עליון)

- איור 9b. מוצא עיצוב אלומה בהשהיית זמן (3D)

- איור 10. ארכיטקטורת חיבורים הדדיים עבור מערך מופע צפוף

- טבלה 1. קשר בין רוחב האות ודגימת-יתר מזערית של מקדמי מסנן

- טבלה 2. מפרטי התכנון

- טבלה 3. משאבים וביצועים של כיוונונים שונים

- טבלה 4. ביצועי פירוק Cholesky DSPBA

- טבלה 5. כמות המקמ”שים והמכפילים של FPGA 28nm ו-20nm