לכידת SYSREF במדויק

ממירים המשתמשים בממשק JESD204B ממשקים נתוני דגימה בקצב גבוה מאוד. כדי להנמיך את רעש המופע במערכת, ממירים אלה משתמשים בדרך כלל בשעון ייחוס, שהוא כמו שעון ההתקן של ה-JESD204, כלומר בקצב הדגימה או מעליו. במקרים רבים, שעון זה נמצא בתחום הגיגה-הרצים. במהירויות כאלה, לענות לדרישות ההתקנה וזמן ההחזקה הוא מאוד מאתגר. כדי להקל על תכנון המערכת, יהיה אולי צורך שהיסט המופע של ה-SYSREF ו/או שעון ההתקן יהיה מתוכנת עבור כל התקן שהוא חלק ממערכת ה-JESD204B.

אחד היתרונות שיש לתת-המחלקה 1 לעומת 2 הוא בכך שהיא משתמשת בשעון מקור סינכרוני. מערכת מתת-מחלקה 2 משתמשת בשעון סינכרוני של המערכת ותיתקל במגבלות תדר מוקדם יותר מאשר אחת שמשתמשת בשעון מקור סינכרוני. דבר זה יוכח כאשר מביטים מקרוב יותר בדוגמאות תזמון של מחלקה 1 ו-2.

אי-ודאות כמיסות דטרמיניסטית

אי-ודאות כמיסות דטרמיניסטית (deterministic latency uncertainty- DLU) היא השיפוע של LMFC במערכת JESD204B והיא נקבעת על-ידי ההפרש בין הלכידה המוקדמת ביותר והמאוחרת ביותר האפשרית של ה-SYSREF במערכת. איור 1 מציג את ה-DLU של המקרה הגרוע ביותר הקורה כאשר דרישות זמני ההתקנה וההחזקה עבור לכידת ה-SYSREF אינן נענות בכל התקן במערכת [1]. דבר זה קורה כאשר שיפוע החלוקה של שעוני המערכת אינו מבוקר ויוצר עד שעון התקן (device clock – DCLK) אחד של אי-ודאות. דבר זה מתווסף לשיפוע החלוקה של

ה- (DSSYSREF כדי ליצור את ה-DLU הכולל).

DSSYSREF הוא ההפרש בין זמן ההגעה של ה-SYREF המגיע ראשון במערכת (לאורך כל ההתקנים במערכת)

וה-SYSREF המגיע אחרון. באיור, TSU הוא 1/2TDCLK ו-THold הוא 1/4TDCLK. ה- (A) המגיע ראשון נלכד בזמן המוקדם ביותר האפשרי DCLKA) בדיוק עונה לדרישת זמן ההתקנה) בשעה

שה-SYSREF () המגיע אחרון נלכד בזמן המאוחר ביותר האפשרי. (DCLKN בדיוק מחטיא את דרישת זמן ההתקנה). כך שה-LMFC’s התואמים הם לא-מכוונים

ב-.

ביישומים רבים, הדרישות עבור DLU הן כאלו שהתרחיש הגרוע ביותר הזה הוא קביל. עבור יישומים אלה, לא יהיה אולי צורך לבחון באדיקות את שיפוע פילוג שעון ההתקן. לוודא שרוחב הפולס של ה-SYSREF הוא ובקרה על שיפוע החלוקה של ה-SYSREF כדי לענות לדרישת תזמון המערכת עשויים להיות מספיקים.

ביישומים בהם שעון ההתקן הנוסף של אי-ודאות איננו קביל, יש לבדוק בחומרה את שיפוע חלוקת השעון של ההתקן כדי לוודא שדרישות התזמון עבור ה-SYSREF נענות בכל התקן של המערכת. מקרה זה מוצג באיור 2 ואי-הודאות נתונה על-ידי המשוואה:

כאשר:

כפי שמוצג במשוואה עבור DLU ליעל, ניתן למזער את ה-DLU על-ידי וידוא שזמני ההתקנה וההחזקה נענים עבור כל זוג של SYSREF/DCLK ועל-ידי מזעור שיפוע החלוקה בתוך הזוגות.

כדי לענות לדרישות ההתקנה וההחזקה, לכל התקן במערכת ה-JESD204B צריך שיהיה הזוג SYSREF/DCLK משלו. בתוך כל אחד מזוגות אלה, אפשר להשתמש בתאום אורך העקבה כדי להבטיח את התזמון. הגבול עבור תאום אורכי העקבות נקבע על-ידי זמן החלון התקף עבור מיתוג ה-SYREF. כמו כן, יש לחבר את מוצא ה-SYSREF עם קצה הלכידה של ה-DCLK ואורך ה-SYSREF צריך להיות גדול מאורך ה-DCLK כפי שנקבע על-ידי דרישת זמן ההחזקה (אם Thold הוא 0, אזי האורכים יכולים להיות שווים).

מאחר שמשתמשים בתאום אורך העקבות, מזעור שיפוע החלוקה בין-הזוגות הוא למעשה זהה עם מזעור שיפוע החלוקה של ה-SYSREF. הגבול של שיפוע החלוקה הזה הוא גבול ה-DLU פחות זמן החלון התקף וניתן לנהל אותו גם באמצעות תאום אורך העקבות. גבול ה-DLU נקבע על-ידי דרישות היישום.

שיטות אלו למזעור ה-DLU מוצגות באיור 3. מאחר שלכל התקן ב-JESD204b יש זוג SYSREF/DCLK עצמי, לענות לדרישות התזמון ללכידת ה-SYREF הוא כמו בכל מערכת המשתמשת בשעון מקור סינכרוני. גבולות התזמון בכל התקן נקבעים בנפרד מכל שאר ההתקנים במערכת.

ה-AD9250 הוא ADC כפול -14ביט, 250MSPS עם JESD204B בעל מוצא נתונים טוריים המוגדר ב-5Gbps. כדי למרב את ביצועי ה-PLL, ה-AD9250 יכול לקבל מהירויות של שעון התקן גבוהות עד כדי 1.5 גיגה-הרץ. דבר זה מספק דוגמה מצוינת כדי להוכיח כיצד עונים לתזמון SYSREF תוך שימוש בתאום אורך העקבות תחת דרישות מערכת ה-DLU המחמירות ביותר [2]. להלן התנאים עבור הדוגמה:

• *

• TSU=500ps and Thold=0ps*

• עבור הדוגמה, ה-DLU max=1 DCLK

() של המערכת *

תאום אורך-העקבה בתוך הזוגות כדי לענות לתזמון ה-SYSREF

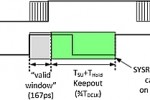

בהתבסס על המפרטים של הדוגמה, ה”חלון התקף” כדי לענות לזמן ההתקנה וההחזקה הוא (667psTDCLK-500ps TSU). זמן הנסיעה הוא הזמן מעזיבת האות את המקור עד להגיעו לקולט (sink). זמן הנסיעה של ה-SYSREF פחות זמן הנסיעה של ה-DCLK צריך להיות פחות מהפרש זמן הנסיעה באינטשים כאשר אנחנו מעריכים שזמן הנסיעה דרך אינטש אחד של חומר Fr4 הוא 167ps לאינטש. כך, עבור כל זוג SYSREF/DCLK במערכת, יהיה צורך למלא את דרישת הניתוב הבאה:

DCLK trace length<SYSREF trace length<DCLK trace length + 1 inch

היענות לדרישה זו תבטיח שהעברת ה-SYSREF תיווצר בתוך החלון התקף כמתואר באיור 4.

תאום אורך-העקבה בין זוגות כדי לענות לגבול ה-DLU

מאחר שגבול ה-DLU נקבע ל-667ps ואנחנו מכירים את הקשר בין גבול ה-DLU ושיפוע חלוקת הזוג (או ה-SYSREF) DSSYSREF, ניתן להשיג בנקל את גבול תאום אורך-העקבה:

כך ששיפוע החלוקה בין-הזוגות לאורך כל זוגות ה-SYSREF/DCLK צריך להיות בתוך ה- [3]:

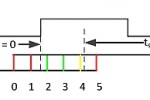

איור 5 מציג את התזמון עבור דוגמה זו. שיפוע החלוקה ה”טובה ביותר” (DSSYSREF) מתייחס למקרה שהיה מאפשר דרישת תאום עקבה-אורך פחות מחמירה.

פתרונות מתקדמים להיענות לתזמון SYSREF וגבול ה-DLU

כמובן, ניתן לפתור את הסוגיה על-ידי שימוש בשעון התקן איטי יותר אשר היה מקל על תאום אורכים. דבר זה היה קורה על-חשבון הקרבת ביצועים אחדים של רעש המופע של המערכת. פיתרון דומה לכך הוא להקל על דרישת ה-DLU אשר היה שומר על היתרון של ביצועי רעש מופע המערכת משופרים. כיצד נקבעת דרישת ה-DLU תלוי ביישום. דבר זה יידון בהמשך בהקשר לדיוק הכמיסות הדטרמיניסטית.

אם דרושים ביצועי רעש מופע משופרים והדרישה של ה-DLU לא ניתנת למיתון, עלול להיות קשה מידי לענות לדרישת הניתוב עבור השיפוע הפנים-ההתקנים SYSREF/DCLK והשיפוע בין ההתקנים (1 אינטש ו-3 אינטש בהתאמה, בדוגמה דלעיל). במקרה זה, דרושה השהית מופע מתכווננת עבור שעון ההתקן ו/או ה-SYSREF. הרזולוציה של ההתאמה צריכה להיות פחות מה”חלון התקף” המבוסס על זמני ההתקנה וההחזקה. בדוגמה זו ה”חלון התקף” הוא 167ps.

FPGAs אחדים עשויים להתקשות בעמידה בדרישות רזולוציה של התאמה קטנה. במקרה זה, ניתן להשתמש במקור שעון מיוחד בעל מוצאים עם מופע מתכוונן עבור ה-SYSREF ו/או שעון ההתקן. איור 6 מראה כיצד ניתן להשהות את ה-SYSREF כדי לענות לדרישות התזמון. באיור, SYSREF מושהית בקפיצות של 60ps. מומלצת בחירת כוונון מופע הממקם את קצה ה-SYSREF קרוב לאמצע החלון התקף. באיור, קצוות ירוקים מראים כיווני מופע טובים וקצוות אדומים מראים כיוונים גרועים. כיוון המופע של 3 הוא באמצע החלון התקף ויש להשתמש בו במקרה זה.

ה-AD9680 של ADI מממשת מעגלי ניטור זמני ההתקנה וההחזקה של SYSREF כדי לסייע בכיוון התזמון היחסי בין ה-SYSREF ושעון ההתקן. על-ידי ניטור שני האוגרים הללו, המשתמש יכול לקבוע באם קיימת סכנה בניצול דרישות התזמון לשם לכידת ה-SYSREF. אם אוגר כלשהו נותן הוראה שגבולות התזמון אינם מספיקים, המשתמש יודע שהוא זקוק להתאמת המצב היחסי של ה-SYSREF ביחס לשעון ההתקן. התאמה זו תיעשה בדוגמה דלעיל או על-ידי התאמת מופע ה-SYSREF ביחס להתקן או בכוונון אורך העקבה של ה-SYSREF ו/או אות שעון ההתקן.

דיוק הכמיסות הדטרמיניסטית

כדי להבין טוב יותר כיצד נקבעת כמיסות דטרמיניסטית של מערכת, דרושה הבנה של היישום. רוב המערכות הדורשות כמיסות דטרמיניסטית צריכות לדעת בדיוק איזו דגימה בזמן מסמלת את תחילת הנתונים המעניינים. שימוש מקובל עבור כמיסות דטרמיניסטית הוא עבור סנכרון ממירים מרובים במערכת אחת. דבר זה מכונה סנכרון רב-שבבי. במערכות אלו, כוונון הדגימה דרוש עבור כל הממירים. לכן, הכמיסות הדטרמיניסטית צריכה להיות “מדויקת לדגימה”. במערכות אלו, ה-DLU צריך להיות ±1/2 שעון הדגימה. היתרון של שעון התקן שהוא כפולה של שעון הדגימה הוא בכך שהוא מפשט את משימת הלכידה של ה-SYSREF בדרך כזו שתהיה מדויקת לדגימה. בדוגמת ה-AD9250, שעון ההתקן הוא 6x שעון הדגימה.

כדי להיות מדויק לדגימה, דרישות ה-DLU של ±1/2 שעון הדגימה מתורגמות ל±3- שעוני התקן. דבר זה מוצג באיור 7. הדוגמה שלנו עבור ה-AD9250 הראתה שאף דרישת ה-DLU המחמירה ביותר ניתנת להיענות בנקל עם היכולת של כוונון מופע ה-SYSREF בכל התקן. כאשר שעון ההתקן הוא כפולה של שעון הדגימה, לכידת ה-SYSREF עבור דיוק הדגימה היא מאוד מפושטת. כאשר קצבי הדגימה עבור הממירים עולים ל-1Gbps או יותר, היכולת להשהיית מופע של ה-SYSREF ושעוני ההתקן נהיית חיונית.

סוגיות פוטנציאליות בלכידת ה-SYSREF

מלבד ההיענות לדרישות זמן ההתקנה וההחזקה של ה-SYSREF ודרישות ה-DLU, ישנן סוגיות פוטנציאליות אחרות העלולות להופיע בהקשר ללכידת ה-SYSREF. לדוגמה, לאחר הדלקת המערכת, יתכן שה-SYSREF יהפוך לפעיל לפני הכוונון של שעוני המערכת. דבר זה עשוי לקרות כאשר משתמשים באות SYSREF קבוע. דבר זה נפתר על-ידי הכללת כושר התכנות בממשק ה-JESD204B המאפשר להתקן להמתין מספר מסוים של קצוות לפני סנכרון השעונים. אופציה תכנותית אחרת עשויה לאפשר למשתמש ל”צייד” את לכידת ה-SYSREF כאשר צפוי קצה תקף. דבר זה מספק בקרה על הזמן לסנכרן עם SYSREF קבוע. להתקני המרה של ADI רבים המשתמשים בממשק JESD204B, כולל ה-AD9625 ו-AD9680 ישנן תכונות כאלה.

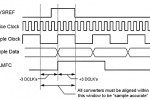

דוגמה אחרת היא ששינויים קטנים ב-SYSREF עשויים לגרום לסנכרון חוזר בלתי הכרחי. דבר זה נפתר על-ידי הכללת יכולת התכנות בממשק ה-JESD204B המאפשר למשתמש להגדיר את החלון התקף מסביב ל-LMFC עבור הקצה של ה-SYSREF. אם ה-SYSREF קורה בתוך חלון תקף זה, אזי ניתן להעריך את המערכת עדיין כמסונכרנת. זוהי תכונה שימושית מאוד מאחר שהרבה יישומים מנטרים אות SYSREF קבוע כדי לקבוע את מצב הקישור. גבול ה-LMFC מושווה ל-SYSREF כדי לקבוע את מצב הסנכרון במקרה זה. ה-AD9680 של ADI מממש תכונה זו כמוצג באיור 8.

תכונות שימושיות אחרות כדי לסייע בלכידת ה-SYSREF הן היכולת לשנות איזה קצה של שעון ההתקן משמש ללכידת ה-SYSREF ואיזה קצה של ה-SYSREF משמש לכוונון ה-LMFC. התקני המרה רבים של ADI המשתמשים בממשק ה-JESD204B כוללים תכונות אלו.

תת-מחלקה 2

במערכת בעלת תת-מחלקה 2, הדיוק של הכמיסות הדטרמיניסטית תלוי ביחס התזמון בין שעון ההתקן ואותות ה-SYNC~ ומגוון נושאים אשר יצרכו את תקציב התזמון, אשר יתוארו להלן. כמו בתת-מחלקה 1, דיוק היישום עבור אי-הודאות של הכמיסות הדטרמיניסטית יהיה קריטי בהגדרת דרישות ההתאמה של אורך העקבה של היישום עבור שעון ה-SYNC~ וההתקן.

לכידה ושיגור ה-SYNC~ – במדויק

האתגר של היענות לדרישות התזמון לשם לכידה מדויקת של ה-SYNC~ הוא בעצם אותו האתגר המוצג בדיון על התת-מחלקה 1 לשם לכידת ה-SYSREF. אולם, מאחר שסכימת השעון בתת-מחלקה 2 היא סינכרונית למערכת, אינך יכול לבצע יותר את ניתוח התזמון בכל התקן לכידה בנפרד מהאחרים והוא הופך לקשה בהדרגה ביישום מרובה-ממירים. לא רק זאת, אלא עליך להיחשב באי-הוודאות הכרוכה בשיגור אות ה-SYNC~. כל התקן במערכת המשתמש בשעון מערכת סינכרוני יצרוך חלק מתקציב התזמון. בין הנושאים הצורכים את תקציב התזמון הם שיפוע חלוקת השעון (DSDCLK), שיפוע חלוקת ה-SYNC~ עבור מערכות מרובות-ממירים, השהיית ההתפשטות של אות ה-SYNC~, דרישת זמן ההתקנה וההחזקה עבור כל JESD204B Tx, והשהיית המוצא של השעון-אל ה-SYNC~ בכל מוצא של JESD204B Rx’s SYNC~.

גבול עליון עבור שעון ההתקן בתת-מחלקה 2

תקן ה-JESD204B מאשר שמימוש תת-מחלקה 2 יחייב גבול בקצב שעון ההתקן בשל סכימת השעון הסינכרוני של המערכת המשמשת. נספח B בתקן קובע שגבול זה הוא 500 מגה-הרץ:

“מאחר ש-SYSREF הוא אות מקור סינכרוני שניתן להפיק בצורה של כוונון מופע מדויק עם שעון ההתקן, מצפים שמתכנן המערכת השואף לפעול בקצבי שעון התקן גבוהים מ-500 מגה-הרץ יעדיף להשתמש בגישה של תת-מחלקה 1”.

הבה ננתח דוגמה מפורטת של תזמון כדי להציג מדוע קיים גבול כזה.

דוגמת תזמון תת-מחלקה 2 מרובה-DAC

נעיין ביישום משדר המשתמש בשני התקני DAC של תת-מחלקה 2 המחוברים להתקן לוגי יחיד כמוצג באיור 9.

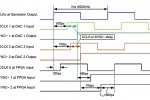

לשם דוגמה, משמש שעון התקן 500 מגה-הרץ. לאותות ה-SYNC~ ו-DCLK יש שיפועי המעגל [4] הרשומים מטה:

Clock to FPGA = 300ps

Clock to DAC1 = 600ps

Clock to DAC2 = 720ps

SYNC~1 to FPGA = 660ps

SYNC~2 to FPGA = 750ps

לפני שנדון בשינויי הריצוד וה-PVT, התזמון הוא כמוצג באיור 10. באיור, תזמון המקרה הגרוע ביותר הוא עם הלכידה של אות ה-SYNC~2 במבוא ה-FPGA. השילוב של השהיית התפשטות DLCK2, השהיית ההתפשטות SYNC~2 והשהיית

clock-to-out של SYNC~2 משאירים 600ps של זמן התקנה לצורכי הלכידה של מבוא ה-FPGA.

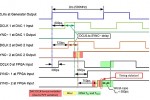

אולם, לאחר שהתווספו זמן ההתקנה, הריצוד ושינויי ה-PVT, עלולה לקרות בקלות הפרה של תזמון כמתואר באיור 11. בדוגמה, זמן ההתקנה הוא 500ps, שינויי ה-PVT מוסיפים עד 300ps והריצוד [6] הוא 150ps. בהגיע אחרון

ה- (SYNC~2), דבר זה יוצר הפרה של התזמון.

בדוגמה דלעיל, אפשר לבצע שינויים באורך העקבה ו/או מופע השעון כדי לפתור את התזמון. אולם, עם עליית תדר ה-DCLK, יהיה יותר קשה להיענות לדרישות התזמון, אף יותר מאשר במימוש תת-מחלקה 1, מאחר שיש להתחשב ביותר משתנים. הפרק 6.4 של תקן JESD204B מכסה בפרוטרוט את נושא תזמון הלכידה של SYNC~.

אי-הודאות של כמיסות דטרמיניסטית בתת-מחלקה 2

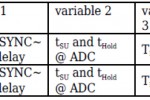

בדיוק כמו בתת-מחלקה 1, אילוצי התזמון ייקבעו על-ידי סיבולת היישום לאי-ודאות של כמיסות דטרמיניסטית. טבלה 1 מסכמת את המשתנים שיש להתחשב בהם כאשר נענים לדרישות התזמון של תת-מחלקה 2 עבור [7] של מערכת.

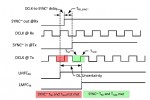

DLU במערכת של תת-מחלקה 2 נקבע על-ידי הקשר בין TCLK-to-SYNC, TPD_SYNC ו-TSU ושיפוע החלוקה של שעוני ההתקן (DSDCLK) במערכת. ביישום בעל ממיר יחיד, ה-DLU של המקרה הטוב ביותר נתון על-ידי המשוואה הבאה ומוצג באיור 12.

באיור, TSU הוא 1/2TDCLK ו-THold הוא 1/4TDCLK . כמוצג, ה-DLCK הוא משופע כדי להתאים להשהיית DCLK-to-SYNC~ והשהיית ההתפשטות SYNC~ ולהיענות בדיוק לדרישת זמן ההתקנה.

המקרה הגרוע ביותר של DLU במערכת תת-מחלקה 2 בעלת ממיר יחיד יקרה כאשר ה-DCLK במשדר איננו משופע דיו ומפר את זמן ההתקנה של קצה הלכידה הראשון הזמין כמתואר באיור 13.

איזו תת-מחלקה היא הטובה ביותר עבור היישום שלך?

בחירת התת-מחלקה שיש להשתמש בה עבור מערכת ה-JESD204B תלויה בצורך שלך בכמיסות דטרמיניסטית, כמה מדויקת היא צריכה להיות אם אתה צריך אותה, ודרישות שעון ההתקן עבור המערכת שלך.

תת-מחלקה 0 היא הקלה ביותר למימוש ויכולה לשמש כאשר אין צורך בכמיסות דטרמיניסטית. אף אם המערכת מרובת-הממירים שלך דורשת סנכרון של הדגימות עבור כל (או חלק) של הממירים, דבר זה ניתן לממש תוך שימוש בשיטת חותמת-הזמן (time-stamp) הנתמכת על-ידי ה-AD9625 וה-AD9680.

אם נתונה היכולת של תת-מחלקה 1 לתמוך בקצבי שעון התקן גבוהים-ביותר ושהם משמשים בממירי קצב דגימה גבוהים, זהו הפיתרון בעל הסיכון הנמוך ביותר עבור מערכות הדורשות את הקצבים המהירים הללו. התקנים ממחלקה 1 יכולים לשמש גם בקצבים נמוכים יותר. אם משתמשים בקצב שעון מתחת ל-500 מגה-הרץ, ההיענות לדרישות התזמון היא ישירה מבלי לדרוש את הכוונוניות במופע השעון.

התקנים ממחלקה 2 יכולים לשמש גם מתחת ל-500 מגה-הרץ. היתרון הקטן בשימוש במחלקה 2 בקצבים נמוכים יותר הוא בכך שהוא מפחית את ספירת ה-IO בהתקן הלוגי ומבטל את הצורך בניתוב של ה-SYSREF לכל אחד מהתקני ה-JESD204B.

[1] במגמה לשמור על תצוגת מושג ה-DLU פשוטה, לא מתחשבים כאן בריצוד השעון ובשינויים בגין התהליך, המתח והטמפרטורה (PVT).

[2] דרישה של ה-DLU שווה לשעון ההתקן מהווה המקרה הגרוע ביותר לשם היענות לתזמון ב-SYSREF.

[3] 500ps הוא השיפוע הגרוע ביותר עבור SYSREF ויש להשתמש בו כדי לקבוע את גבול התאמת אורך העקבה

[4] 300ps~~1.8 inches of PCB trace

[5] שינויי PVT במוצא ה-SYNC~ ושני המוצאים של השעון

[6] ריצוד ב-DLCK ו-SYNC~

- איור 1. אי-ודאות של כמיסות דטרמיניסטית במקרה הגרוע ביותר

- איור 2. DLU בשעה שהוא עונה לזמן ההתקנה וההחזקה עבור SYSREF מזעור אי-הוודאות של הכמיסות הדטרמיניסטית

- איור 3. ניתוב ה-SYSREF/DCLK עבור מערכת JESD204B בעלת 3 התקנים. דוגמה של תזמון ה-SYSREF תוך שימוש ב-AD9250

- איור 4. היענות לדרישת התזמון של ה-SYREF/DCLK

- איור 5. היענות לדרישת שיפוע החלוקה הבין-זוגי

- איור 6. השהיית מופע מיתכנתת עבור SYREF כדי לענות לתזמון ניטור זמן התקנה והחזקה של SYSREF

- איור 7. דרישת “דיוק הדגימה” עבור לכידת ה-SYSREF

- איור 8. חלון הניטור של ה-SYSREF

- איור 9. יישום מרובה-DAC בתת-מחלקה 2

- איור 10. תזמון SYNC~/DCLK ביישום מרובה-DAC של תת-מחלקה 2

- איור 11. הפרת תזמון SYNC~/DCLK ביישום בתת-מחלקה 2 מרובה-DAC

- איור 12. SYNC~ בתת-מחלקה 2 – תזמון לכידה עבור יישום של ממיר יחיד: המקרה הטוב ביותר של DLU

- איור 13. זמן הלכידה SYNC~ תת-מחלקה 2 עבור יישום של ממיר יחיד: DLU במקרה הגרוע ביותר

- טבלה 1. משתני תזמון המשפיעים על DLU של תת-מחלקה 2