חברת ARM שרבות כבר דיברנו וכתבנו עליה, לא עוצרת אפילו לא לרגע כאשר בשנת 2013 נמכרו בעולם יותר מ-10 מיליארד רכיבים עם אחד מהליבות של ARM והחברה טוענת שהיא רק בתחילת הדרך.

עד היום משפחות ה-ARM היו מחולקות לשלושה עם הבחנה ברורה ביניהם כפי שניתן לראות בתמונה מספר 1 (בעמוד הבא):

ליבות CortexMx לעולם ה-Embedded

ליבות CortexRx לעולם ה-Real Time

וליבות CortexAx לעולם ה-High End Embedded, Mobile, Tablets and Servers

ה”אינטרנט של הדברים” IoT – Internet of Things יוצר צורך לליבות חדשות משופרות עבור פיתוחים שעונים חכמים, צמידים חכמים, אלקטרוניקה לבישה וגם השילוב של הבית החכם (לדוגמא: Google Nest – Thermostat תרמוסטט חכם) עם הדרישה הגוברת לשילוב של מסכים עם

HMI – () בעיקר סביב הרצון שכל מערכת תהיה פשוטה כמו הטלפון החכם כלומר מסך על בסיס Android או iOS עם גרפיקה משופרת תלת-מימדית.

היסטורית, ליבת ה-CortexM משמשת כליבה האולטימטיבית בעולם המיקרו-בקרים (Micro Controllers) הכוללים זיכרון פנימי והתקנים פריפריאליים דיגיטליים ואנלוגיים וכאשר הלקוחות היו צריכים יותר כוח עיבוד, אוטומטית היו בוחנים את פתרונות המיקרו-מעבדים (Micro Processors) מבוססים ליבת CortexAx כגון CortexA8 ו-CortexA9 על מערכת הפעלה Linux אבל היום, כאשר ARM הכריזה על ליבת CortexM7 החדשה, ההבחנה בין המשפחות נעשית יותר מטושטשת מכיוון שעם יכולות עיבוד כה גבוהות, לקוחות שבעבר בחנו פתרונות High End ללא צורך, יכולים להישאר עדיין עם בסיס מיקרו-בקר ולא לעבור למיקרו-מעבד.

בתמונה מספר 2 (בעמוד הבא) ניתן לראות את משפחות ה-CortexMx השונות בהתאם. בשנת 2010, ARM חשפה את ליבת CortexM4 על יסודות ליבת CortexM3 עם הרחבות שונות המותאמים לעיבוד אותות דיגיטלי ( – Digital Signal Processing) וכמו כן תוסף תמיכה בנקודה צפה (- Floating Point Unit). פתרון זה היה פתרון ייחודי שיצר עולם של חדשנות בצורת Cost Performance. היום על ליבת CortexM7 הרחיבה ARM את צינורי העיבוד הפנימיים משלוש (single-issue) לשש (superscalar in-order).

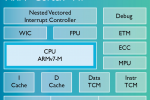

בתמונה מספר 3 ניתן לראות את המבנה הפנימי של הליבה החדשה.

כפי שניתן לראות התווספו

שתי בלוקים של זיכרון מטמון: I-Cache () ,D-Cache

() שנפוץ רק במערכת מיקרו-מעבדים (Micro-Processors).

כמו כן פס הנתונים החדשים שנקרא AXI-M שהוא בעצם בס (Bus) של 64 ביט: 64-bit AXI AMBA4 שנועד לעזור בביצוע חישובים מתמטיים וגרפיים.

חברת STMicroelectronics הכריזה על זמינות ראשונה של רכיבים המבוססים על ליבת CortexM7 החדשה של ARM שנקראת STM32F7xx (תמונה מספר 4) ובכך נפתחה אפשרות של לקוחות על בסיס אלפא Alpha Customers לבחון את היכולות החדשים ולעזור לחברת ST לעצב את הפתרון לפני הגעתו לייצור המוני ברבעון שני של שנת 2015.

המשפחה החדשה STM32F7 הינה המשפחה הראשונה בעולם שמיוצרת על בסיס CortexM7 ובעצם מוכיחה את היכולות העוצמתיות החדשות בעולם המיקרו-בקרים.

הבדיקות הפופולאריות היום להוכיח את יכולות העיבוד (“Horse Power”) מתבצעות על ידי ה “CoreMark” ו-DMIPS ונכון לרגע זה הנתון שהתקבל הינו: /1000CoreMark 428 DMIPS בתדר של 200Mhz.

רק לשם השוואה בין המשפחות הקיימות של ST ניתן להבחין בשיפור העצום בביצועים:

STM32F2xx – 398 CoreMark , Cortex-M3 in 90nm eFlash

STM32F4xx – 608 CoreMark , Cortex-M4 in 90nm eFlash

STM32F7xx – 1000 CoreMark Cortex-M7 in 90nm eFlash,

השוואה זו בעצם מסבירה ללקוחות הרבים המשתמשים בפתרונות STM32 של ST ולהם יש צורך ביותר ביצועים אך לא על חשבון ההספק כי ניתן לעבור ממשפחה למשפחה, להשתמש בקוד הקיים ואפילו באותה אריזה ולהרוויח.

מבחינת ההספק, ST סיפקה גם את ההבדלים בין משפחת STM32F4x מבוססת CortexM4 לבין המשפחה החדשה STM32F7 המבוססת על הליבה החדשה CortexM7 (תמונה מספר 5)

STM32 F7 7 CoreMark/mW at 1.8 V = 72 mA at 180 MHz

STM32 F4 7 CoreMark/mW at 1.8 V = 47 mA at 168 MHz

פרטים על המשפחה החדשה :

The STM32 F7 series unleashes the new Cortex M7 core:

AXI and multi-AHB bus matrix for interconnecting Core, peripherals and memories

Two general purpose DMA controllers and dedicated DMAs for Ethernet, high-speed USB On-The-Go and the Chrom-ART graphic accelerator.

Peripheral speed independent from CPU speed (dual clock support) allowing system clock changes without impacting the function of the peripherals

Even more peripherals, such as two serial audio interfaces (SAI) with SPDIF output support, three I2S half-duplex with SPDIF input support, two USB OTG with dedicated power supply and Dual Quad SPI interface

320KBytes of SRAM with scattered architecture:

240 Kbytes of universal data memory

a 16 Kbytes partition for sharing data over the bus matrix

64 Kbytes of Tightly-Coupled Data Memory (DTCM) for time critical data handling (stack, heap…)

16 Kbytes of Tightly-Coupled Instruction Memory (ITCM) for time critical routines

4 Kbytes of backup SRAM to keep data in the lowest power modes.

חברת ארו (Arrow) בשיתוף עם חברת HandsOnTrainning הישראלית וחברת Hilf הגרמנית פיתחו קורסים ייחודים וראשוניים בעולם המבוססים על הליבה החדשה של ARM ה-CortexM7. הקורסים הראשוניים יהיו עבור מהנדסי האפליקציות של ארו בגרמניה ולאחר מכן בשאר אירופה (כולל ישראל) עם התמקדות במשפחה החדשה של ST

ה-STM32F7 ובכך יחלו בבחינת ההתקשרות עם הלקוחות הראשונים שיבססו את המוצרים החדשים שלהם עם המשפחה החדשה.

ההכרזה הרשמית של המשפחה החדשה של ST תהיה בתערוכת Embedded World בנירנברג גרמניה ולאחר מכן חברת ארו ושותפיה יחלו בהטמעת הטכנולוגיה החדשה לכלל לקוחותיה כולל מגוון רחב של קורסים וסמינרים המבוססים על STM32F7.

- תמונה 5

- תמונה 4

- תמונה 3

- תמונה 2

- תמונה 1

- אמיר שרמן, מנהל עיסקי וטכנולוגי EMEA ב-Arrow