עם הוספת חלקים למעגלים משולבים – תדר רדיו (RFIC), עולים מקורות רעש צימוד נוספים, דבר ההופך את ניהול אספקת המתח ליותר ויותר חשוב. מאמר זה מתאר כיצד רעש אספקת מתח עלול להשפיע על ביצועי המעגלים המשולבים – תדר רדיו. מְמָצֶה האפנון הקואדראטורי (quadrature בעל החוג נעול המופע phase-locked loop – () המשולב והמתנד מבוקר – מתח, הvoltage-controlled oscillator () משמשים כדוגמה, אך התוצאות ישימות באופן די נרחב למעגלים משולבים – תדר רדיו רבי ביצועים אחרים.

רעש ספק הכוח עלול להוריד מאיכות הליניאריות על ידי יצירת תוצרים מעורבלים בממצה האפנון ולהרע את הרעש הפאזי בחוג נעול המופע – PLL ובמתנד מבוקר – מתח, ה-VCO. הערכת מתח מפורטת מלווה בתכנונים של המתח המומלץ באמצעות שימוש בווסתים בעלי נפילה נמוכה – low-dropout regulators ווסתי מיתוג.

באמצעות האספקה הכפולה ושילוב תדר רדיו ברמה גבוהה, ה-ADRF6820 מספק כלי אידיאלי לדיון. הוא משתמש בליבת מערבל פעילה דומה כמו מְמָצֶה האפנון הקואדראטורי ADL5380, והליבות הזהות PLL/VCO כמו ה-ADRF6720, כך שהמידע המוצג ניתן ליישום ברכיבים אלו. בנוסף, ניתן ליישם את תכנון אספקת המתח בתכנונים חדשים הדורשים אספקת מתח של 3.3 וולט או 5.0 וולט בעלי צריכת מתח דומה.

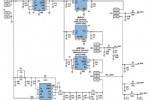

ממצה האפנון והסינתיסייזר ADRF6820 המוצג באיור 1, מתאים באופן אידיאלי למערכות תקשורת של הדור הבא. ההתקן עשיר התכונות מכיל ממצה אפנון I/Q רחב – פס ובעל ליניאריות גבוהה, PLL מקטעי – N משולב, ו-VCO רב – ליבתי בעל רעש – נמוך – פאזה. כמו כן, הוא משלב מתג תדר רדיו 2:1, בּאַלוּן תדר רדיו ניתן לכוונון, מָנחֶת משרעת תדר רדיו הניתן לתכנות, ושני LDOים. המעגל רב השילוב – תדר רדיו – RFIC, זמין באריזת LFCSP 6 X 6 (מ”מ).

רגישויות אספקת מתח

החלקים המושפעים ביותר על ידי רעש אספקת המתח הם ליבת המערבל והסינתסייזר. הרעש המוכנס לתוך ליבת המערבל יוצר תוצרים לא רצויים המורידים את איכות הליניאריות ואת התחום הדינמי. דבר זה קריטי במיוחד עבור מְמָצֶה האפנון הקואדראטורי כיוון שהתוצרים של הערבול בעל התדר הנמוך מתרחשים בתוך הפס המעניין אותנו. באופן דומה, רעש אספקת המתח עלול לפגוע ברעש הפאזי של

ה-PLL/VCO. השפעת תוצרי הערבול הלא רצויים והרעש הפאזי אשר נפגע, משותפת לרוב המערבלים והסינתסייזרים, אך הדרגה המדויקת של הפגיעה נקבעת על ידי הארכיטקטורה וסידור השבב. הבנה של רגישויות אלו של אספקת המתח, מאפשרת תכנון יציב יותר אשר מְמָטֵב ביצוע ויעילות.

רגישויות מְמָצֶה האפנון הקואדראטורי

ADRF6820 משתמש בליבת ערבול אקטיבי מסוג תא ג’ילברט (Gilbert cell) בעלת איזון כפול, כפי שמוצג הדבר באיור 2. איזון כפול, פירושו כי יציאות ה-LO וה-RF, מופעלות באופן דיפרנציאלי.

לאחר דחיית הרמוניקות מסדר גודל גבוה על ידי מסנן, פלט המערבל הנובע מכך, הינו הסכום וההפרש של קלט ה-LO וה-RF. ביטוי ההפרש, הקרוי גם תדר IF, מצוי בפס שהוא מענייננו, והוא האות הרצוי. ביטוי הסכום מצוי מחוץ לפס, והוא מסונן.

באופן אידיאלי, רק אותות ה-RF וה-LO הרצויים מובאים לליבת המערבל, אך מקרה זה נדיר. רעש אספקת המתח עשוי להיצמד אל תוך קלט המערבל והוא מופיע כשלוחות ערבול. בתלות במקור צימוד הרעש, המשרעת היחסית של שלוחות הערבול, עשויה להשתנות. איור 3 מראה מדגם של ספקטרום פלט מערבל והמקום שם תוצרי הערבול עשויים להימצא עקב צימוד רעש אספקת המתח (power-supply). באיור, CW מייצג גל רציף, או אות סינוסואידלי, אשר נצמד לפס אספקת המתח. הרעש עשוי להיות רעש השעון הנובע מווסת ממתג בתדר של 600kHz או 1.2MHz, למשל. רעש אספקת המתח עלול לגרום לשתי בעיות שונות: אם הרעש נצמד לפלט המערבל, טון הגל הרציף (CW) יופיע בפלט ללא תרגום תדר; אם הצימוד מתרחש בקלט המערבל, טון הגל הרציף יאפנן את אותות ה-RF

וה-LO, דבר אשר ייצור תוצרים ב-IF± CW.

תוצרי העירבול הזה, עשויים להיות

קרובים לאות ה-IF הרצוי, וכך, האפשרות לסנן אותם הופכת לקשה, ובעקבות כך, ההפסד בתחום הדינמי הינו בלתי נמנע. דבר זה נכון במיוחד עבור המְמָצים הקואדראטוריים, כיוון שפס הבסיס שלהם מורכב ומרוכז סביב זרם – ישר.

רוחב הפס של מיצוי האפנון של ADRF6820 משתרע מזרם – ישר עד ל-600MHz. אם ליבת העירבול מוזנת על ידי מווסת ממתג עם רעש המצוי בתדר של 1.2MHz, אזי יתפתחו תוצרים לא רצויים בתדר IF ±1.2MHz.

רגישויות סינתסייזר התדירות

ההפניות בסוף המאמר מספקות מידע בעל ערך אודות השאלה כיצד רעש אספקת המתח משפיע על המעגלים המשולבים – PLL ו-VCO. העקרונות הללו ישימים לגבי תכנונים אחרים בעלי אותה ארכיטקטורה, בעוד תכנונים לא זהים יזדקקו להערכת אספקת המתח משל עצמם. למשל, המעגל המשולב LDO בתוך ספק הכוח VCO של ADRF6820 מציע חיסון רב יותר נגד רעש מאשר אספקת מתח מ-PLL אשר אינו משתמש ב-LDO משולב.

תחומי אספקת המתח של ADRF6820 וצריכת זרם

על מנת לתכנן את הפתרון של ניהול אספקת המתח, בדוק קודם את תחומי אספקת המתח של ה-RFIC על מנת לקבוע מאיזה תחום כל בלוק של RF מקבל אספקת מתח, את צריכת המתח של כל תחום, אופני הפעולה המשפיעים על צריכת המתח, ואת דחיית אספקת המתח של כל תחום. באמצעות שימוש במידע זה, ניתן לאסוף נתונים אודות הרגישות של ה-RFIC.

לכל אחד מהבלוקים הפעילים העיקריים של ADRF6820, יש פין מתח משלו. שני תחומים מקבלים מתח ממקור אספקת מתח של 5 וולט. ה-VPMX מזין את ליבת המערבל, וה-VPRF מזין את הקצה הקדמי של תדר הרדיו ואת מתגי הקלט. התחומים הנותרים, מוזנים ממקור אספקת מתח של 3.3 וולט. VPOS-DIG מזין מעגל משולב LDO, אשר מפיק 2.5 וולט להזנת ממשק ה-SPI, המאפנן Σ-Δ של ה-PLL, ולהזנת המחלקים . VPOS-PLL מזין את מעגלי ה-PLL, כולל את תדר קלט הייחוס (REFIN), את גלאי תדר הפאזה (PFD), ואת משאבת הטעינה (). VPOS-LO1 ו-VPOS-LO2 מזינים את מסלול ה-LO, כולל את מגבר פס הבסיס ואת ייחוס עיוות הזרם – הישר. VPOS-VCO מזין מעגל משולב LDO אחר, אשר מפיק 2.8 וולט להזנת ה-VCO הרב-ליבתי.

ה-ADRF6820 ניתן לקינפוג במספר אופני פעולה. הוא צורך פחות מ-1.5mW באופן פעולה רגיל עם LO של 2850MHz. הקטנת זרם העיוות מקטינה את צריכת המתח וגם את הביצועים. הגדלת זרם העיוות של המערבל, הופכת את ליבת המערבל ליותר ליניארית ומשפרת את IIP3, אך פוגעת בנתון הרעש ומגדילה את צריכת המתח. אם נתון הרעש הינו בעל חשיבות עיקרית, אפשר להקטין את זרם עיוות המערבל, וכך, להקטין את הרעש בתוך ליבת המערבל ולצמצם את צריכת המתח. באופן דומה, למגברי פס הבסיס בפלט, יש אפשרויות הנעת זרם משתנות עבור עומסי פלט בעלי התנגדות נמוכה. עומסי פלט בעלי התנגדות נמוכה דורשים הנעת זרם גבוה יותר וצורכים יותר מתח. גיליון הנתונים מציג טבלאות המראות את צריכת המתח עבור כל אופן פעולה.

הליכי מדידה ותוצאות

צימוד רעש על גבי פס המתח, מייצר טונים לא רצויים בגל הרציף – CW, וב-IF±CW. על מנת לחקות את צימוד הרעש הזה, הפעל טון גל רציף לכל פין מתח ומדוד את המשרעת של תוצר העירבול המופק ביחס לטון הגל הרציף. רשום מדידה זו כדחייה של אספקת המתח ביחידות של dB. דחיית המתח משתנה עם התדר, לכן, מתח את תדר הגל הרציף לאורך פס תדרים מ-30kHz עד ל-1GHz על מנת לקלוט את ההתנהגות. דחיית המתח על גבי הפס הנדון, קובעת האם יש צורך בסינון.

ה-PSRR מחושב כלהלן:

CW PSRR ביחידות dB = משרעת CW בקלט (dBm) – ה-CW הנמדד והמוזן בקלט ה-,

PSRR ביחידות dB = משרעת CW בקלט (dBm) – ה-IF ± CW הנמדד והמוזן בקלט ה-(I/Q (dBm,

(IF ± CW) ביחידות dBm = dBm, בעוד לטונים של הגל הרציף המאופננים סביב הגל הנושא יש משרעות שווות.

הקמת המעבדה

איור 4 מציג את הקמת המעבדה. חבר מתח של 3.3 או 5 וולט זרם – ישר למנתח הרשת על מנת ליצור אות סינוסואידאלי רציף בעל קיזוז של 3.3 או 5 וולט. הפעל מתח זה לכל אחד מפסי המתח על גבי ה-RFIC. שני מחוללי אות מספקים אותות קלט RF ו-LO. מדוד את הפלט על גבי מנתח ספקטרום.

הליך המדידה

משרעת התוצרים הלא רצויים של העירבול, תלויה בדחיית אספקת המתח של השבב, ובגודל ובמיקום של קבלי הצימוד ולוח ההערכה. איור 5 מציג את משרעת הטון IF + CW בפלט בהינתן אות סינוסואידאלי של 0dB. ללא קבלי ביטול צימוד, משרעת הטון הלא רצוי הייתה בין 70dBc ו-80dBc. גיליון הנתונים ממליץ על קבל 100pF צמוד להתקן שעל גבי הלוח ועל קבל של 0.1µF בצדו האחורי של הלוח. ניתן לראות את התהודה של קבלי ביטול הצימוד הללו בעקומה. המעבר ב-16MHz נובע מהתהודה של קבל ה-100pF בעל ההשראה הפרזיטית של 2nH הנובעת משני הקבלים. המעבר ב-500MHz נובע מהתהודה של קבל ה-100pF בעל ההשראה הפרזיטית של 1nH.

תוצאות

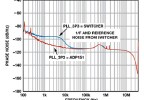

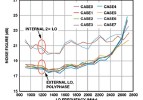

משרעות האות המפריע (CW) על גבי פס המתח ועל גבי האותות המאופננים (IF± CW) נמדדו בפלט פס הבסיס. לפס המתח הנבדק, הוכנס רעש, בעוד יתר ספקי המתח נשארו נקיים. איור 6 מציג את משרעת הטון של (IF±CW) כאשר הוכנס אות סינוסואידאלי לפין המתח והאות נמשך מתדר של 30kHz לתדר של 1GHz. איור 7 מציג את ההזנה מטון ה-CW לפלט פס הבסיס.

ניתוח

העקומות מספקות נתונים בעלי ערך לא ישוער אודות רגישויות אספקת המתח בכל פין מתח. ל-VPOS-PLL יש את הדחייה הגרועה ביותר של אספקת מתח, ולכן, הוא מהווה את צומת האספקה הרגיש ביותר. פין מתח זה מספק מתח למעגלי ה-PLL, כולל תדר קלט הייחוס, גלאי תדר הפאזה, ומשאבת הטעינה. בלוקים רגישים אלו של פונקציות קובעים את הדיוק ואת ביצועי הפאזה של אות ה-LO, כך שכל רעש הצמוד על גביהם משליך ישירות על הפלט.

על פי אותו היגיוּן אפשר לטעון כי גם אספקת המתח של ה-VCO היא צומת קריטי. העקומות מראות כי ל-VPOS-VCO יש דחייה הרבה יותר טובה מאשר לVPOS-PLL. זוהי התוצאה של ה-LDO הפנימי המספק למעשה מתח ל-VCO. ה-LDO מבודד את ה-VCO מהרעש על גבי הפין החיצוני וגם מספק לו צפיפות ספקטרלית בעלת רעש קבוע. לספק הכוח של ה-PLL אין LDO, דבר ההופך אותו לפס המתח הרגיש ביותר. לכן, בידודו מפני צימוד הרעש הפוטנציאלי הנו דבר קריטי עבור ביצועים מיטביים.

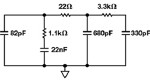

מסנן לולאת ה-PLL מפחית תדירויות CW גבוהות, כך שהרגישות על גבי הVPOS-PLL היא נמוכה בתדירויות נמוכות והיא משתפרת באיטיות עם משיכת התדר מתדר של 30kHz לתדר של 1GHz. בתדירויות גבוהות יותר, משרעת הטון המפריע מונמכת ורמת המתח המוכנס לתוך ה-PLL נמוכה באופן משמעותי. לכן, VPOS-PLL מראה דחיית מתח טובה יותר בתדר גבוה מאשר בתחומי המתח האחרים. רכיבי מסנן הלולאה קוּנְפֶגוּ עבור 20kHz, כפי שמוצג באיור 8.

תכנון אספקת המתח

עם הבנה טובה של צריכת המתח המירבית של ADRF6820 במודים השונים שלו ושל הרגישויות של כל תחום מתח, הפתרונות לניהול מתח תוכננו באמצעות שימוש בווסתי מיתוג וגם ב-LDOים על מנת לקבוע את היתכנות שני הפתרונות. ראשית, מקור של 6 וולט הובא לרמה של 5 וולט ושל 3.3 וולט עבור פסי המתח של ADRF6820. איור 9 מציג את תכנון המתח עבור אספקת מתח של 5 וולט עבור VPMX ועבור VPRF.

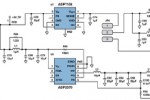

ה-ADP7104 CMOS LDO יכול לספק זרם עומס של עד 500mA. ווסת המיתוג היורד ADP2370 בעל – זרם – שקט יכול לפעול בתדירויות של 1.2MHz או 600kHz. לפלט ווסת המיתוג, נוסף סינון, על מנת להנמיך את רעש המיתוג. ה-ADP2370 יכול לספק זרם עומס של עד 800mA. ניתן להזין את פס המתח של 5 וולט של ADRF6820 על ידי ADP7104 או על ידי ADP2370. צימוד וסינון נוספים מיושמים לכל פין אספקת מתח.

איור 10 מציג את תכנון המתח עבור 3.3 וולט. מתח המקור הוא עדיין 6 וולט, אך LDO נוסף מוריד את המקור למתח ביניים לפני שהוא מווסת שוב למתח של 3.3 וולט. השלב הנוסף נדרש על מנת לצמצם את הפסדי המתח, כיוון שמקור של 6 וולט המווסת ישירות כלפי מטה לרמה של 3.3 וולט, יפעל ברמת יעילות מירבית של 55%. אין צורך בשלב ביניים עבור מסלול ווסת המיתוג, כיוון שארכיטקטורת אפנון רוחב הדופק (PWM) מצמצמת למינימום את הפסדי המתח.

התכנון של 3.3 וולט אִפשר יותר אפשרויות ניסוי. בנוסף למיקור פס המתח של 3.3 וולט באמצעות LDO או באמצעות ווסת מיתוג, לפס המתח של VPOS-PLL קיימות יותר אופציות LDO ולפס המתח VPOS-DIG יש LDO אופציונלי מבוּדָד. כיוון שאספקת המתח של PLL היא הרגישה ביותר, פתרונות אספקת מתח אלו אכן נוסו, כל אחת מהן עם רעש פלט שונה: ה-ADP151 עם CMOS LDO בעל הרעש האולטרה – נמוך ובעל מתח של 3.3 וולט עם רעש פלט של ; ה-ADP7104 עםCMOS LDO בעל הרעש הנמוך ובעל מתח של 3.3 וולט עם רעש פלט של , והווסת היורד 3.3 וולט ADP2370. ברצוננו לקבוע את הרמה הגבוהה ביותר של רעש אספקת מתח אשר עדיין תקיים את ביצועי רעש הפאזה הנדרשים. האם ה-LDO בעל הביצועים הגבוהים ביותר, ועם הרעש הנמוך ביותר הוא בעל נחיצות הכרחית?

ה-ADP121 עם CMOS LDO בעל רעש נמוך ובעל מתח של 3.3 וולט נוסה אף הוא על גבי פס המתח של VPOS-DIG, על מנת לקבוע אם רעש דיגיטלי ישפיע על הביצועים. פס המתח הדיגיטלי נוטה להיות רועש יותר מאשר אספקת מתח אנלוגית, עקב המיתוג אשר על גבי ממשק ה-SPI. ברצוננו לקבוע אם המתח הדיגיטלי של 3.3 וולט ידרוש LDO משל עצמו או האם ניתן לחבר אותו ישירות לאספקת המתח האנלוגית.

ה-ADP121 נבחר כפתרון העלות הנמוכה.

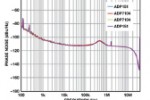

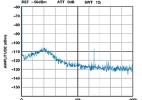

מסקנות והמלצות לתכנית אספקת מתח

עבור VPOS-PLL, פס אספקת המתח הרגיש ביותר, ה-LDO של ADP151 בעל העלות הנמוכה, משיג את אותו רעש פאזה כפי שעושה זאת ה-LDO בעל הרעש הנמוך, רוב הביצועים, של ADP7104, המוצג באיור 12. חטוטרת הרעש נגרמת על ידי ווסת המיתוג, ואת זאת ניתן לראות בפלט שלו, כפי שניתן לראות באיור 13. באופן זה, ה-VPOS-PLL יכול לסבול רעש של עד ללא פגיעת רעש פאזה משולב, אך לא ניתן להשתמש בווסת מיתוג על מנת לספק מתח לפין זה. לא מושגת שום הטבה על ידי שימוש ב-LDO בעל רעש נמוך, רב – ביצועים.

ביצועים טובים פאזה – רעש מתקיימים כאשר ווסת מיתוג או LDO מספקים מתח לפסי אספקת המתח הנותרים, כפי שמוצג הדבר באיור 14. ניתן לחבר את הפינים של אספקת מתח 5 וולט, VMPX ו-VPRF, ולספק להם מתח באמצעות מקור אספקה אחד. ניתן לחבר גם את הפינים של אספקת מתח 3.3 וולט, VPOS-LO1 ,VPOS-LO2, VPOS-VCO, ולספק להם מתח באמצעות מקור אספקה אחד. ה-VPOS-DIG אינו דורש LDO עצמאי וניתן לחבר אותו למקור אספקת מתח אנלוגי של 3.3 וולט.

עם מקור מתח של 6 וולט, תכנון אספקת המתח המומלץ המוצג באיור 15, כולל את ה-LDOים 5 וולט של ADP7104 ואת ה-3.3 וולט של ADP7104. פתרון זה משתמש רק

ב-LDOים, כיוון שמתח המקור קרוב למתחי האספקה הנדרשים. יעילות האספקה היא בסדר, כך שהעלות הנוספת של רכיבי סינון ווסתי מיתוג נמנעת.

עם מקור מתח של 12 וולט, תכנון אספקת המתח המומלץ המוצג באיור 16 כולל שני ווסתי מיתוג ו-LDO אחד. מקור המתח גדול הרבה יותר ממתחי האספקה הנדרשים, כך שנעשה שימוש בווסתי מיתוג על מנת לשפר את יעילות האספקה. ניתן לספק מתח לכל הפינים מווסתי המיתוג, למעט הפינים של ה-VPOS-PLL. ניתן להשתמש ב-ADP7104 או ב-ADP151 עבור VPOS-PLL.

הפניות

Circuit Note CN0147. Powering a Fractional-N Voltage-Controlled Oscillator (VCO) with Low Noise LDO Regulators for Reduced Phase Noise. Analog Devices, Inc., 2010.

Collins, Ian. Integrated PLLs and VCOs (Part 2). Radio-Electronics.com, Nov 2010.

Modulators/Demodulators

Linear Regulators

Switching Regulators

קוי לוּוּ הינה מהנדסת יישומי תדר רדיו (RF) בחברת אנאלוג דיבייסז (Analog Devices) מאז יוני 2000. קוי קיבלה את תואר ה-B.S.E.E. שלה מהמוסד הפוליטכני וורססטר (Worcester Polytechnic Institute) בוורססטר, מאסאצ’וסטס, ארה”ב, בשנת 2000, ואת תואר ה-M.S.E.E. שלה באוניברסיטת נורתאיסטרן (Northeastern University) בבוסטון, מאסאצ’וסטס, ארה”ב, בשנת 2005.

- איור 1. תרשים מלבנים מפושט ADRF6820

- איור 2. מערבל אקטיבי מסוג תא ג’ילברט בעל איזון כפול

- איור 3. מעמד ספקטרום פלט מערבל עם צימוד רעש אספקת מתח

- איור 4. הקמת מדידת ADRF6820 PSRR

- איור 5. השפעות תהודת קבלי צימוד על IF ± CW

- איור 6. PSSR של טון ה – IF ± CW

- איור 7. ה-PSSR של טון ה-CW

- איור 8. לולאת מסנן ה-PLL מקונפגת עבור רוחב פס לולאה של 20kHz

- איור 9. תכנון אספקת מתח 5 וולט

- איור 10. תכנון אספקת מתח 3.3 וולט

- איור 11. רעש פאזה משולב באמצעות שימוש ב-ADP151 ו-ADP7104

- איור 12. רעש פאזה משולב באמצעות שימוש ב-ADP151 ו-ADP2370

- איור 13. ספקטרום הפלט של ה-ADP2370

- איור 14. נתוני רעש מתג כנגד LDO

- איור 15. תכנון אספקת מתח מומלץ עבור מקור מתח של 6 וולט

- איור 16. תכנון אספקת מתח מומלץ עבור מקור מתח של 12 וולט