PCI-Express () הוא עמוד השדרה של המערכות המורכבות של ימינו הזקוקות לתקשורת נתונים מהירה והספק גדול. PCI-Express נמצא בשימוש נרחב ביישומים שונים כגון כרטיסי מחשבים, כרטיסים גרפיים, במערכות רכב, רישות, ביישומים תעשייתיים ובמוצרי צריכה. ביישומים במכוניות, PCIe משמש לתקשורת נתונים המגיעה במהירות גבוהה מאוד מעיבוד גרפי ווידיאו בזמן אמת. הוא שימושי מאוד במערכות סיוע מתקדמות לנהיגה (ADAS).

מאחר וכיום, כאשר מוקד תשומת הלב בענף הרכב עובר לממשקים אלקטרוניים סדרתיים במהירות גבוהה, מאמר זה דן באופני האימות של PCIe במערכות-על-שבב (SoCs). האימות הפונקציונלי הוא רק חלק ממתודולוגיית האימות השלמה הדרושה לאימות ממשקים במהירות גבוהה כגון PCIe. מאמר זה עוסק בתחומים אשר האימות הפונקציונלי רלוונטי עבורם ובמיוחד בתרחישים השונים העלולים להוות מחסום פוטנציאלי בתכנון מערכת באיכות גבוהה.

- תרשים 1

- תרשים 2

הקדמה ל-PCIe

PCI Express הוא הדור השלישי של אפיקי קלט-פלט עתירי ביצועים המשמשים לחיבור התקנים היקפיים ביישומים כגון פלטפורמת מחשוב ותקשורת. PCI Express הוא אפיק קלט-פלט מקשר ומקיף הניתן לשימוש בפלטפורמות מובייל, תחנות עבודה שולחניות, שרתים, מחשוב משובץ ותקשורת.

PCIe משמש ליצירת התקשורת בין התקני לוח-אם היקפיים כגון כרטיס גרפי או כרטיס את’רנט ליחידת העיבוד המרכזית ולזיכרון. הוא גם מאפשר להתקנים היקפיים נוספים כגון כרטיס גרפי חיצוני ודיסק קשיח חיצוני להתחבר באופן חלק להתקני לוח האם בצורה פשוטה של plug-and-play.

PCIe הוא אפיק טורי מבוסס מנות המספק חיבור אותות dual-simplex מהיר, עתיר ביצועים, מנקודה לנקודה בין התקנים המחוברים זה לזה. הנתונים מועברים מהתקן על גבי מערך אותות אחד ומתקבלים במערך אותות שני.

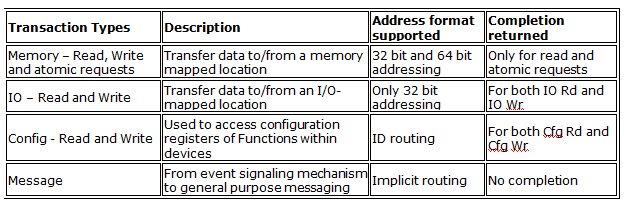

טבלה 1

החיבור והנתיב של PCIe: חיבור PCI Express הוא החיבור הפיזי בין שני התקנים. נתיב (lane) כולל צמדי אותות בכל כיוון. חיבור x1 כולל נתיב אחד או צמד אותות דיפרנציאלי אחר בכל כיוון וארבעה אותות בסך הכל. חיבור x32 כולל 32 נתיבים או 32 צמדי אותות בכל כיוון ו-128 אותות בסך הכל.

זמן השעון והמהירות של PCIe: בחיבור לא קיים אות שעון. כל מנה שצריכה לעבור על גבי החיבור כוללת בתי מידע. כל בית מקודד לסמל של 10 סיביות. כל הסמלים הם בעלי מעברי אפס-אחד. הרסיבר עושה שימוש ב-PLL לשחזור השעון ממעברים ל-1 ומ-1 ל-0 של זרם הסיביות הנכנס. PCIe מהדור הראשון תומך ב-2.5GTs, מהדור השני ב-5GTs ומהדור השלישי ב-. PCIe מהדור הראשון והשני משתמשים בקידוד 8/10 סיביות ואילו PCIe מהדור השלישי משתמש בסכמת קידוד של 128/130 סיביות.

המהירות ורוחב החיבור המרביים הנתמכים תלויים ביישום ובתרחיש השימוש של המערכת-על-שבב שבה הם משתמשים.

הטופולוגיה של PCIe

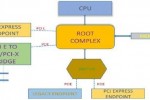

Root Complex () משמעותו השורש של היררכיית קלט/פלט המחברת את יחידת העיבוד המרכזית/זיכרון לקלט/פלט.

נקודת הקצה (EP) מתייחסת לסוג הפונקציה שיכולה להיות Requester או Completer של טרנסאקציית ה-PCI באופן עצמאי או כמייצגת התקן שאינן PCI Express (ואינו התקן PCI או CPU מארחת), לדוגמה, בקר גרפי המחובר ל-PCI Express או בקר מארח ב-USB עם PCI Express.

מתג הוא המערך הלוגי של מספר רב של התקני גישור וירטואליים מ-PCI ל-PCI. גשר PCI Express to PCO/PCI-X מספק חיבור בין PCI Express fabric לבין היררכיית PCI/PCI-X.

תרשים 1 מדגים fabric יחיד שאליו נתייחס כהיררכיה – המורכב מ-Root Complex , מספר רב של נקודות קצה (התקני קלט/פלט), מתג וגשר PCI Express to PCI/PCI-X, שכולם מחוברים באמצעות חיבורי PCI Express.

ה-PCI בנוי בארכיטקטורה של שלושה רבדים לתקשורת בין שני התקנים. הרבדים הם:

שירותי רובד הטרנסאקציות: רובד הטרנסאקציות מאתר בחיבור flow control credits עבור TLPs, מחולל TLPs מבקשות בליבת ההתקן, וממיר TLPs מבקשות שהתקבלו לבקשות מליבת ההתקן.

שירותי רובד חיבור הנתונים: רובד חיבור הנתונים אחראי לחילופי מידע אמינים עם המקביל לו בצדו הנגדי של החיבור.

שירותים ברובד הפיזי: הרובד הפיזי אחראי לאתחול הממשק, בקרת תחזוקה ומעקב סטטוס (Reset/Hot-Plug).

טרנסאקציות PCIE ופורמט הכתובות:

PCIe תומך בטרנסאקציות posted (P) ,non-posted () ובטרנסאקציות השלמה (Cpl). טרנסאקציות posted הן טרנסאקציות שלא נדרשת עבורן השלמה, כגון MWr ו-MSG. טרנסאקציות non-posted הן טרנסאקציות שעבורן מוחזרת השלמה כגון כל הקריאות (MRd/IORd/IOWr). (ראו טבלה 1)

כאשר יש זרם נתונים, הרובד הפיזי הוא הראשון שנכנס לפעולה. לאחר מכן עובר החיווי לרובד חיבור נתונים שנכנס לפעולה ולאחר מכן רובד הטרנסאקציות נכנס לפעולה.

במנת נתונים, כמוצג לעיל (תרשים 2) בצד ה-TX, מוספים השדות על-ידי כל רוב ובצד ה-RX כל רובד מסיר את השדות בהתאמה. זרם הרבדים והנתונים דרך הרבדים מתואר בתרשים 2.

- תרשים 3

- תרשים 4

ה-PCIe במערכות על שבב ברכב

כבר יותר ממאה שנה שהמכוניות ממשיכות ומתפתחות ככל שיצרני הרכב מגלים דרכים לשיפור הנהיגה, היעילות, הבטיחות והביצועים של מכוניות. אחד החידושים שהושקו לאחרונה בתעשיית הרכב הן מערכות עזר מתקדמות לנהג (ADAS) שפותחו על מנת להעניק בטיחות גבוהה יותר למכונית ולנהג ונהיגה טובה יותר. מערכת זו כוללת מאפייני מניעת תאונות באמצעות התראה לנהג או באמצעות תפיסת שליטה אוטומטית על הרכב. מאפיינים אלה כוללים תאורה אוטומטית, בקרת שיוט המתאימה את עצמה לנסיבות, בלימה אוטומטית, התראות GPS, התראה על סכנות לנהג, תיקון נהיגה בנתיב וניתוח של שטחים מתים. על-פי רוב, מערכות אלו מבוססות על מערכות צילום/ראייה, טכנולוגיית חיישנים וכו’. במערכות ראייה יש צורך בעיבוד בזמן אמת של נתוני תמונות ווידיאו הנכנסים מסביבת הרכב. מאחר והנתונים מתקבלים במהירות גבוהה מאוד ובכמויות גדולות מאוד, אנו זקוקים לממשק מהיר שיטפל בכל עיבוד. ה-PCI Express, עם המהירות והתפוקה הגבוהות שלו, מספק פתרון אמין לדרישה זו של טיפול בזמן אמת בנתונים הנכנסים במהירות גבוהה. ה-PCI-Express פועל במהירויות GT/s (משתנות בהתאם לדורות ה-PCIe השונים). תרחיש שימוש אופייני של PCI-Express המכונית הוא תקשורת בתת-המערכות LCD במושב האחורי.

תחומים שיש לכסות באימות PCIe במערכת-על-שבב: PCIe הוא IP מורכב התומך במספר גדול של מאפיינים. על-פי המגמה הכללית בתעשיית ה-VLSI, מבצעים אימות של ה-IP לפני שילובו במערכות על שבב. לפיכך עלינו לפרט את המאפיינים שמן ההכרח לאמת ברמת ה-SoC. אימות של כל אחד ואחד מהמאפיינים הפנימיים של ה-IP ברמת ה-SoC אינו מומלץ מסיבות ברורות. כעת עולה השאלה מה עלינו לאמת מנקודת המבט של המערכת על שבב. בהיותו interconnect הפועל במהירות גבוהה, ל-PCIe יש בעיות משלו, הן מנקודת מבט פונקציונלית והן מנקודת מבט חשמלית. איננו יכולים לאשר מערכת על שבב אשר יש בה PCIe מבלי לאמת באופן מלא את המאפיינים הפונקציונליים והחשמליים של ה-IP. בממשקים מהירים מאוד, יש לתקף את שלמות הרובד הפיזי ולשים לב ש-reflections, cross-talk, פליטות ותופעות אחרות מתרחשות כולן במגבלות המותרות. הן אינן אמורות לפגום ברמת האות עד למצב שבו האות לא יהיה ניתן לזיהוי על-ידי החיבור השותף. דיון באימות חשמלי אינו בתחום עיסוקו של מאמר זה ולכן נתמקד לעת עתה באימות פונקציונלי בלבד. גם מנקודת מבטו של מהנדס האימות הפונקציונלי ומאחר ומדובר בממשק מהיר מאוד, יש להריץ סימולציות RTL וכן סימולציות ברמת השער. סימולציות RTL מסייעות לזהות בעיות פונקציונליות בעוד שסימולציות ברמת השער מסייעות באיתור בעיות תזמון. לכן עלינו להריץ את הבדיקות בשני סוגי הסימולציות. הרשימה שלהן מפרטת את המאפיינים שעלינו לבדוק בשביל לכסות את רמת ה-SoC כולה מנקודת מבט פונקציונלית.

1. הפונקציונליות בין רובד היישומים (ליבת המערכת/מעבד והרגיסטרים החיצוניים) וה-IP של ה-PCIe: ככלל, רובד היישומים מוטמע ב-SoC באופן חיצוני ל-IP של ה-PCIe שמספק צוות ה-IP. עלינו לאמת את המאפיינים הנשלטים על-ידי הרגיסטרים ברובד היישומים ואת ה-glue logics. אלה עשויים להצריך החלפה של סוג ההתקן (מ-Root Complex ל-End Point וההיפך); חלק מהמאפיינים של PHY כגון de-emphasis, תנודות מתח; סיביות סטטוס המגיעות מה-PCIe כגון סטטוס החיבור, המצב הנוכחי של ה-LTSSM וכו’.

2. הפונקציונליות בין ה-crossbar (אינטרקוננקט) של המערכת לבין ה-PCIe IP: תמיכה בגשר AXI או AHB כלולה בדרך כלל ב-PCIe IP כך שהוא מסוגל לתקשר עם ממשק המערכת המקביל. עלינו לאמת את שני המצבים, PCIe כ-slave ומסטרים שונים המתקשרים עימו באמצעות ה-crossbar. יש צורך לבצע סוגים שונים של גישות קריאה וכתיבה (8 סיביות, 16 סיביות, 32 סיביות, 64 סיביות וכו’). מסטרים שונים יכולים להיות ליבות, DMA וכו’. ה-Slaves השונים יכולים להיות DDR RAM, זיכרון פלאש, RAM המערכת, RAM גרפי, וכו’.

3. הפונקציונליות של הפסיקה PCIe IP יכול לתמוך במספר רב של סוגי פסיקות לבקר הפסיקות. יש לנו פסיקות שגיאה להודעות שגיאה פטאליות שאינן ניתנות לתיקון. יש לנו פסיקות להודעות INTx או למנות MSI שהתקבלו כ-Root Complex. יש לנו גם timeouts כגון timeout של השלמה הנשלח כפסיקה לבקר הפסיקות. עלינו לבדוק את תרחיש יצירת הפסיקה ואת הקישוריות שלה לבקר הפסיקות. יכולות גם להיות פסיקות שונות במצבים שונים כגון Link Up (חיבור פעיל), Link Down (חיבור מושבת), power down (הפסקת חשמל), וכו’.

אימות PCIe המערכת-על-שבב מורכבת:

את הפונקציונליות המפורטת לעיל ניתן לאמת בסביבת SoC בשני שלבים:

1. מצב Loopback

2. שימוש ב- Verification IP/BFM מצב LOOPBACK: במצב זה אנו מחברים את מסלולי ההעברה של ה-PCIe, שהינם פלט של ה-SoC, למסלולי הקליטה של ה-PCIe, שהינם קלט של ה-SoC. בדרך זו, כל הנתונים שנשלחו מה-SoC נקלטים בחזרה ב-SoC. באופן זה אנו יכולים לבדוק רק מאפיינים מסוימים משום שה-PCIe יכול להיות רק RC או EP בזמן נתון. לכן, המאפיינים המצריכים את שניהם אינם ניתנים לאימות במצב loopback. על-פי רוב, המאפיינים הניתנים לאימות באמצעות מצב זה הם קישוריות הזיכרון, קישוריות ה-system crossbar וחלק מקישוריות רובד היישומים. תרשים 3 מציג את החיבור למצב loopback ואת האפיק שאליו מתבצעת גישה בעת ביצוע טרנסאקציית זיכרון.

האפיק שאליו מתבצעת גישה בטרנסאקציה המתוארת בתרשים 3 הוא:

SYSTEM_CORE → CROSSBAR → PCIE → LOOPBACK → PCIE → CROSSBAR → MEMORY

לבסוף, הליבה קוראת את תוכן הזיכרון על מנת לבדוק שנתוני ה-loopback שנשלחו באמצעות ה-PCIe Tx זהים לאלה שהתקבלו באמצעות ה-PCIe Rx.

שימוש ב-IP/BFM לאימות: במצב זה משתמשים ב-IP אימות המסוגל לתקשר עם ה-SoC ולשלוח ולקבל טרנסאקציות בממשק ה-PCIe. כפי שניתן לראות בתרשים 4, אנו משתמשים ב-BFM הפועל כמו שותף חיבור ל-PCIe המשולב ב-SoC. ה-BFM זקוק לדרייבר ולמוניטור. מטרת הדרייבר היא להפעיל (drive) את הטרנסאקציה ב-PCIe interconnect. מטרת המוניטור לאסוף את הנתונים המגיעים בממשק הקבלה של ה-BFM ולחולל נתונים הקשורים למנה שהתקבלה. בדרך זו ניתן לאמת את הפונקציונליות הזקוקה לשותף חיבור מרוחק. חלק ממאפיינים אלה כוללים פסיקות (legacy (interrupts כגון INTx, MSL, L1/L2 entry וכו’. תרשים 4 מראה את החיבור של ה-BFM והאפיק שאליו מתבצעת גישה במהלך טרנסאקציה.

האפיק שאליו מתבצעת גישה לעיל הוא:

SYSTEM_CORE → CROSSBAR → PCIE → BFM (Transaction path)

BFM → PCIE (Response path)

במקרה שסוג המנה הוא פסיקה כגון INTx, ה-PCIE שולח פסיקה לליבת המערכת וליבת המערכת משרתת את הפסיקה.

סיכום

בהתחשב בכך ש-PCIe מהווים כיום חלק קריטי במערכות על שבב לתקשורת מהירה ואמינה, ועל מנת לחסוך במשאבים ולהבטיח את איכות התכן, עלינו לתקף מאפיינים מסוימים של ה-PCIe ברמת ה-SoC. ניתן לאמת מאפיינים כגון קישוריות master-slave בסיסית במצב loopback ואת המאפיינים המצריכים מעורבות של שותף חיבור באמצעות Verification IP/BFM.