ה- – “Field-Programmable Gate Array” מורכב מיחידות לוגיות הניתנות לתכנות ומרשת של אמצעים לחיבור ולניתוק בין היחידות השונות. בטעינת ה-FPGA מקבלות היחידות הגדרה לאופי פעולתן, והן מתחברות ליחידות אחרות, בצורה שמממשת את המעגל הלוגי הכולל. רכיבי FPGA יכולים לשמש למגוון פונקציות, החל מלוגיקות פשוטות כגון שערים לוגיים וכלה ביכולות מורכבות.

ה-FPGA התחיל את דרכו כמקביל ומתחרה ל-CPLD אך ככל שהגודל, היכולות, ומהירות הפעולה של ה-FPGA גדלו, גדל גם נתח השוק של רכיבים מסוג זה. כיום מקובל למצוא רכיבי FPGA כמערכות מבוססי CPU . כיום ה-FPGA מגיעים לממדים של 6 מיליון LE שכל LE שווה ערך לכ-60 מיליון Gate Logic בעולם ה-ASIC.

ה-FPGA התחיל את דרכו כמקביל ומתחרה ל-CPLD אך ככל שהגודל, היכולות, ומהירות הפעולה של ה-FPGA גדלו, גדל גם נתח השוק של רכיבים מסוג זה. כיום מקובל למצוא רכיבי FPGA כמערכות מבוססי CPU . כיום ה-FPGA מגיעים לממדים של 6 מיליון LE שכל LE שווה ערך לכ-60 מיליון Gate Logic בעולם ה-ASIC.

שש שנים לאחר המצאת (Circuit Integrated) ב-1965 תבע גורדון מור את הכלל שהפך ל”חוק מור”, הצופה כי בכל שנתיים מוכפלים מספר הטרנזיסטורים המיוצרים על מצע סיליקון אחד. בדומה ל”חוק מור” טכנולוגית ה-I/O Signals התפתחה לתחום מהירויות של ג’גה ביט לשניה אשר אילצה שימוש באותות דיפרנציאלים ושילוב של שעון ומידע יחד. ההתמודדות עם דרישת המהירות ומגבלות הטכנולוגיה הובילה ליצירת ארכיטקטורת מערכת Point2Point Serial, צמצום השימוש בארכיטקטורת ה-Multidrop Bus ומעבר מערוצי מידע מקביליים לטוריים. ככל ש”חוק מור” המשיך להגביר את כמות הלוגיקה והכנסת מעבדים מהפשוטים NIOS ,microblaze עד ARMs חזקים מכל משפחתיהם, והדרישות הבלתי פוסקות להגיע לביצועים שמאלצים את תעשיה הסמיקודקטור לרדת לממדים הכמעט בלתי אפשריים מבחינת פסיקאית,ומידי שנה ושנה האתגר נפרץ ומצליחים לרדת בממדים של הטרנזיסטורים, והיום ה-FPGA מגיעים ל-16nm ואפילו ל-14nm.

זאת הסיבה שחברות ה-FPGA נרכשות על ידי החברות המובילות של תעשיית הסמיקודקטור.

שוק הסמיקודקטור נמצא במאבק תמידי על ארבעה פרמטרים:

1. Performance

2. power efficiency

3. density

4. system integration

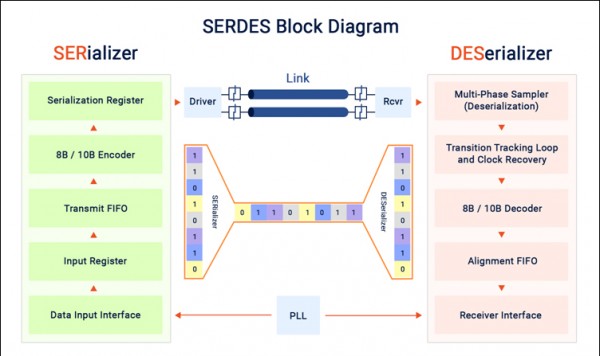

שתי סיבות הובילו למציאת פתרון של קווי תקשורת מהירים SerDes, RapidIO, SFI האחת, דרישה של ריבוי הממשקים לעולם החיצון, והשניה, הצורך הבלתי פוסק לקצב הנתונים החל מ-1 ג’גה ועד 40 גיגה בתים לשנייה, ויש להם מפות דרכים המובילות למאות גיגה בתים לשנייה. המושג SerDes, מעגלי Serializer/ Deserializer ממיר DATA סריאלי לנתונים מקבילים, או ממיר BUS המקביל ל-Bit Stream. דוגמא מצוינת היא החלפת ה-32 ביט של PCI 64 שהשיג 2.112 מגה ביט לשניה, עם נתיב יחיד PCI Express המשיג קצב נתונים כולל של 4 ג’גה ביט לשניה באמצעות רק 4 חוטים ב-2.5GHz. במילות פשוטות, פרוטוקולי SerDes מאפשר קצבי נתונים מאוד גבוהים על חוט אחד מאשר בסיס רחבים בטכנולוגיות הישנות.

ישנם שני סוגים בסיסיים של ממשקי SerDes: מקור סינכרוני (SS) פרוטוקולים לשחזור נתוני שעון פרוטוקולים (CDR). ההבדל הבסיסי הוא כיצד משחזרים את השעון (Clocking). סינכרוני מקור ממשקים יש אות שעון דיסקרטית המלווה את הנתונים המועברים (Data). נטיק מתמודדת באתגרים לתכנון נכון של מערכות שדורשות ממשקים מהירים עבור יישומי תקשורת אופטית, עיבוד תמונה, וידאו, עיבוד אותות, גרפיקה ותקשורת.

קיימים עשרות טכנולוגיות עם ממשק SerDes מרובה-נתיב ליישומיים שונים למשל ממשק Serdes Framer Interface : הממשק יכול לשמש ליצירת קשר ממודולים שונים בממשקים מהירים מעבר ל-40 גיגה ביט לשניה. לדוגמא רשת תחבורה אופטית (OTN) או מודול SONET/SDH FRAMER לבין מודול FEC; OTN או SONET/SDH FRAMER לבין SerDes חיצוני. חיבורים אלו מהווים את הממשק הטיפוסי של מערכות תקשורת אופטיות שקצב הנתונים נע בין 80 גיגה ביט לשניה ל-120 גיגה ביט לשניה.

ה-SerDes משתמשים בקידוד קו B8/B10 או בקידודי קו יעילים יותר כגון קידוד קו B64/B62 למשל RapidIO Gen3. בגלל קצב הנתונים המקסימאלי של האות החשמלי שהוא פחות משיעור הנתונים האופטי, נדרש מספר רב של ערוצים ולכן לדוגמא הפרוטוקול SFI מוגדר לתמוך ב-BUS נתונים רחב n סיביות. וכך ניתן להעביר נתונים בקצב הנדרש.

ה-FPGA מאפשר לנו בצורה קלה לתכנן את ה-SerDes דרך ממשקים ה-MegaWizard עבור ALTERA או LogiCORE™ IP עבור XILINX שמאפשר לקבוע את תצורה של אחד או יותר מערוצי השידור. וגם מאפשר להפעיל את תכונת תצורה דינמית בין הערוצים בתלות דרישות המערכת.

Jack Edery is a General Manager

VLSI and IOT Division.

18 years of experience in the semiconductor and design industries, solid experience in managing complex design and verification projects, with extensive experience in ASIC & FPGA development and design methodology. Manager at Defense Industries, Samsung and Intel Israel.