מוצג תכנון מבוסס על מפענח דיגיטלי וממשק JESD204B עבור מערכות קליטה על-קולית מרובות-ערוצים. התכנון מקטין את קצבי הנתונים ומפשט עד 80% את ניתוב הכרטיס בין הקצה הסופי האנלוגי (Analog Front End -AFE) והמעגלים של עיבוד דיגיטלי. בנוסף, המערכת העל-קולית יכולה לבצע יותר מטרות תכנון, דוגמת השימוש ב-Field Programmable Gate Arrays יותר זולים ופחות יעילים מבחינה מחשבית, יוצר-קרניים מבוסס-תוכנה, ועיבוד רב-קווי עבור אופני הדמיה בזמן-אמת 4D מתקדמים.

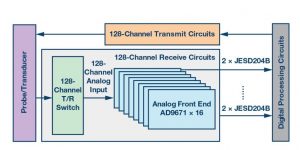

איור 1. דיאגרמה מלבנית של מערכת על-קולית בעלת 128 ערוצים

מבוא

מתכנני מערכות הדמיה על-קוליות צריכים להיאבק כדי למלא את הדרישה לאיכות תמונה יותר גבוהה תמיד המבוטאת על-ידי משתמשים בכל תחום האבחון הרפואי. אחת מטכניקות-המפתח לשיפור איכות התמונה היא שיפור היחס אות-לרעש של ערוץ הקליטה. בשעה שמספר ערוצי הקליטה במערכת מוכפל, היחס אות-לרעש היה אמור להשתפר ב-3dB בתיאוריה. לכן, הגדלת מספר ערוצי המערכת הפכה לשיטה הקלה ביותר והיעילה ביותר כדי לחזק את היחס אות-לרעש.

כיום, 128 ערוצים הפכו לתצורת המיינסטרים עבור ציוד רפואי על-קולי באיכות גבוהה, ו-192 או יותר ערוצים יהפכו למגמה הבאה עבור מערכות משוכללות.

עם גידול מספר הערוצים, קצבי הנתונים בין הקצה הסופי האנלוגי וקבוצת העיבוד הדיגיטלי בקצה הסופי גדלו בהתאם. מספר ערוצים גבוה יותר גם יוצר עלייה דומה במספר ממשקי ההתקנים במעגל הדיגיטלי, בספק העיבוד, העלויות ומורכבות התכנון של כל מעגל המקלט. לדוגמה, רוב מערכות ההדמיה העל-קוליות משתמשות בטכניקות של יצירת קרן בתדר רדיו (Radio Frequency-RF) כאשר קצב הנתונים במוצא נקבע במלואו על-ידי הרזולוציה, קצב הדגימה ומספר הערוצים של הממיר אנלוגי-לדיגיטלי (analog-to-digital converter – ADC). באותו הזמן, הקצה האנלוגי משתמש לרוב בממשקי מוצא בעלי Signaling. אוקטלי דורש 8 זוגות של מוליכי נתונים LVDS וזוג של שעון נתונים ושעון מסגרת כל אחד. עבור מערכת בעלת יותר מ-128 ערוצים, קיימים מספר משמעותי של חיבורי נתונים וחיבורים פיסיקליים.

מאמר זה מציג לראשונה פיתרון תכנון של ערוץ קליטה על-קולי מבוסס על AFE אוקטלי עם ממשק מפענח דיגיטלי וה-JESD204B המשמש כדוגמה. שימוש בגישה זו פותר ביעילות את קשיי התכנון הנגרמים על-ידי קצבי הנתונים הגדולים והחיבורים הפיסיקאליים המורכבים של המערכת כמצוין לעיל.

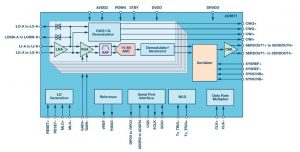

איור 2. דיאגרמה מלבנית פונקציונלית של ה-AD9671

ארכיטקטורת המערכת

מערכת על-קולית מורכבת מחיישן (מתמר), מעגל שידור, מעגל קליטה, מעגל עיבוד דיגיטלי סופי, מעגל בקרה, מודול תצוגה וכו’. איור 1 הוא הדיאגרמה המלבנית של נתיב שידור/קליטה של מערכת על-חוטית עם ממשק JESD204B.

מודול העיבוד הדיגיטלי כולל לרוב Field Programmable Gate Array (FPGA) המפיק את צורות הגל המתאימות לתצורת הזרם ופרמטרי הבקרה של המערכת, וההזנה של מעגל השידור והמעגל בעל מתח גבוה המפיק מתח גבוה כדי להפעיל את המתמרים העל-קוליים. המתמר העל-קולי עשוי לרוב מ-Piezoelectric Ceramic Transduce (PZT). הוא ממיר אות המתח לגל על-קולי החודר לגוף האדם בשעה שהוא מקבל את ההדים הנוצרים על-ידי העצמים והרקמות של הגוף.

ההדים המגיעים מומרים לאות מתח ומשודרים למעגל מיתוג שידור/קליטה (transmitting/receiving – T/R). המטרה הראשונית של מעגל המיתו T/R היא למנוע את אות השידור בעל מתח גבוה להזיק לקצה הסופי של מעגל הקליטה בעל המתח הנמוך. אות המתח האנלוגי המגיע מוגבר ונחשף להתניית האות וסינון לפני העברתו ל-ADC המשולב של ה-AE שם הוא מומר לנתונים דיגיטליים. האות הדיגיטלי משודר לאחר מכן דרך ממשק של JESD204B אל החלקים הדיגיטליים בקצה הסופי של העיבוד המתאים במטרה ליצור את התמונה העל-קולית. ערוץ הקליטה מורכב ממעגל מיתוג T/R בעל 128 ערוצים, 16 יחידות ערוצים אוקטליים על-קוליים של ה-AFE עם מפענח דיגיטלי ו-FPGA בעל ממשק JESD204B.

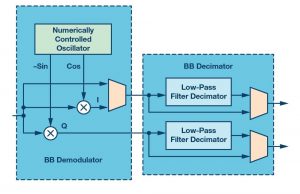

איור 3. דיאגרמה מלבנית של מפענח דיגיטלי

על-קולי אוקטלי בעל מפענח דיגיטלי וממשק JESD204B

ה-AFE העל-קולי האוקטלי בעל מפענח דיגיטלי וממשק ה- JESD204B יוצרים את הבסיס של מערכת קליטה על-קולית זו. היא מכילה שמונה ערוצי מגבר בעל שבח משתנה (Variable Gain Amplifier – VGA) עם מגבר בעל רעש נמוך (Low Noise Amplifier -LNA), מפענח גל רציף I/Q בעל דחייה הרמונית עם סיבוב מופע מיתכנת, מסנן (Anti-Aliasing (AAF), ADC 14-ביט, מפענח דיגיטלי ו-decimator עבור עיבוד נתונים והפחתת רוחב הפס, וממשקי JESD204B. איור 2 הוא דיאגרמה מלבנית פונקציונלית של ה-AD9671.

המפענח הדיגיטלי מורכב ממפענח פס צר (baseband) מורכב ממפענח פס צר ו-decimator פס צר. המפענח ממיר כלפי מטה את אות ה-RF לאות ניצב בעל פס צר. דגימת היתר הנוספת (excess oversampling) מופחתת על-ידי decimator. איור 3 הוא דיאגרמה מלבנית של מפענח דיגיטלי.

ממשק JESD204B

המוצא הדיגיטלי של ה-AD9671 עונה ל-תקן JEDEC JESD204B, Serial Interface for Data Converters. ה-AD9671 תואם לממשקים בעלי נתיבים יחידים, כפולים או ניצבים. הוא יכול להתחבר ל-FPGA בעל קצב נתונים מרבי של 5.0Gbps.

תכנון ויישום המערכת

תכנון מעגל המקלט של המערכת העל-קולית רב-ערוצית AD9671 מובא בפרק זה והיתרונות של השימוש במפענחים דיגיטליים וממשקי JESD204B מנותחים בהמשך.

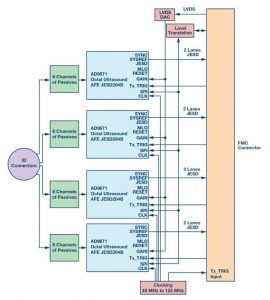

איור 4. דיאגרמה סכימטית ברמה עילית של מעגל הקליטה

תכנון מעגל המקלט

דיאגרמה עילית של סכימת מודול קליטה של מקלט בעל 32 ערוצים מוצגת באיור 4, שניתן לנצל כדי לבחון את ייתכנות המערכת המבוססת עלה-AD9671. עם ארבעה מודולים כגון אלה, ניתן לעצב מעגל קליטה של מערכת על-קולית .

ניתן להשתמש במודול זה כדי לבצע לכידה ועיבוד הנתונים כמו גם את עיבוד האותות העל-קולייים ויצירת התמונה על-ידי חיבור ל-FPGA דרך מחבר FMC מיוחד.

ניתוח יישום של מפענח דיגיטלי

עבור מערכת על-קולית בעלת 128 ערוצים, אם -14ביט משמש עם קצב דגימה של 40MSPS, ומשתמשים באלגוריתם יוצר קרניים RF, אזי, קצב הנתונים בין מוצא ה-ADC וה-FPGA יוצר הקרן הוא 14*40*128=71.68Gbps.

היתרונות של שימוש במפענח דיגיטלי מנותחים להלן.

המפענח פס צר של האות RF מבצע פענוח ניצב. אפשר לעשות זאת על-ידי הכפלת אות ה-RF הדיגיטלי בעל המוצא של ה-ADC עם אות סינוסי מרוכב עם תדר מפענח שיכול להיות קרוב לתדר המרכזי של המתמר העל-קולי לשם המרה כלפי מטה של התדר המרכזי בערך ל-0 הרץ. אות המוצא הוא אות מרוכב המיוצג על-ידי ה-I וה-Q שלו. התדר המרכזי של החיישן וכל האותות בתחומי התדר בעלי עניין מוזזים כלפי מטה בערך ל-0 הרץ, מרכיבי התדר הבלתי רצויים מסוננים החוצה עם המסננים וה-decimator כדי לשמור על מידע התחום השימושי ליצירת התמונות העל-קוליות.

בשביל מתמר חיישן בעל תדר מרכזי של 3.5 מגה-הרץ, אחרי פענוח פס הבסיס וה-decimation, עם מוצא נתונים I ו-Q בפורמט -16ביט, קצב הנתונים הוא עתה =14,336Gbps. בהשוואה ל-71.68Gbps המקורי, קצב הנתונים הופחת ב-80% אף עם ערוצי I ו-Q נמצאים במוצא בו-זמנית.

ניתוח יישום ממשק

במונחים של AFE ו-ADC שוטפים ביישומי מערכת על-קולית רב-ערוצית, LVDS החליף את ממשק המוצא המקבילי. אולם עבור מערכת על-קולית בעלת 128 ערוצים או יותר, הכמויות הגדולות של חיבורי מוליכי LVDS עבור מוצא ה-ADC מהוות עדיין כאב-ראש עבור מהנדסי התכנון. עם LVDS, ישנם 10 זוגות מוליכים עבור AFE אוקטלי אחד במערכת על-קולית שוטפת. עבור מערכת על-קולית בעלת 128 ערוצים, 128/8*10=160 זוגות של מוליכי נתונים ושעון LVDS דרושים להיות מחוברים אל ה-FPGA.

היתרונות של השימוש בממשק JESD204B מנותחים להלן.

מאחר ש-JESD204B משתמש בצורה של מוצא דיגיטלי בעל 16-ביט ומשתמש בקידוד 8B/10B, קצב הנתונים במוצא עבור AFE אוקטלי בעל רזולוציה של 14-ביט, 40MSPSADC קצב הדגימה הוא 20*40*8=6.4Gbps. קצב הנתונים המרבי בכל נתיב של ממשק AD9671 JESD204B הוא 5.0 Gbps, כך שדרושים רק 2 זוגות של נתיב הנתונים כדי לבצע מוצא נתנוני ADCAFE בעלי 8 ערוצים. כך שעבור מערכת על-קולית בעלת 128 ערוצים, רק 128/8*2= 2 זוגות של נתיבי נתונים במוצא דרושים בהשוואה ל-160 זוגות של מוליכי LVDS; 80% מניתוב הממשק הפיזיקאלי מבוטלים.

סיכום

תכנון מערכת על-קולית רב-ערוצית מבוססת על AD9671, AFE אוקטלי בעל מפענח דיגיטלי וממשק JESD204B מוצג במאמר זה. יתרונות היישום של שימוש ב-AFE כזה בעל מפענח דיגיטלי וממשק JESD204B במערכת על-קולית מנוצחים ביעילות בהתאמה. בהשוואה לרוב תכנוני יצירת קרן RF ומבוססי-ממשק LVDS, הן קצב הנתונים והן ניתוב הממשק בין החזית האנלוגית וחלקי העיבוד הדיגיטלי מוקטנים ב-80%.

אם שתי השיטות משולבות יחד בניתוח, החיבורים הפיסיקאליים היו מוקטנים אף יותר. לכן, תכנון המערכת המוצג במאמר זה יכול לפשט ביעילות את תכנון המעגל ואת מורכבות עיבוד התוכנה על-ידי צמצום שטח הכרטיס הדרוש עבור ניתוב ממשק הנתונים, דרישת המורכבות החישובית כמן גם עלויות תכנון המערכת.

סימוכין

1. Analog Devices Inc. JESD204B Octal Ultrasound AFE with Digital, AD9671 datasheet, http://www.analog.com/media/en/technical-documentation/data-sheets/AD9671.pdf.

2. Saad Ashraf, AD967x Digital Processing Overview and System Consideration. Analog Devices Inc., 2012.

3. JEDEC Standard, Serial Interface for Data Converter, JESD204B (July 2011), JEDEC Solid State Technology Association, http://www.jedec.org/.