דרישות הנעה רק הולכים וגדלים עם הזמן:

- יותר כוח

- יותר מהירות

- יותר דיוק

על מנת להצליח ולספק את הדרישות צריכת האנרגיה גודל, אם בגלל דרישת כוח גדול יותר, או יותר מהירות, או בגלל שנדרש להתמדה במקום ובמהירות של התנעה בדיוק גבוה יותר.

עם כל זה המקום הפנוי לדרייבר הולך וקטן.

זה נשמע כבעיה,אבל עם הטכנולוגיה המשתפרת כל העת יש לנו היום כלים ורכיבים שמאפשרים לנו לעמוד במשימה.

בוא נתקוף ונפתור כל בעיה לגופה:

- 1. יותר הספק, פחות נפח

מזמן אנו מתכננים גריברים בשיטת PWM ולא לינארית על מנת לבקר מנועים וכך אנו חוסכים פיזור אנרגיה (בצורת חום) אומנם עדיין עם אנחנו צריכים לספק 1kw, ויש לנו יעילות של כ 90% משתמע מכך שכ100W מבוזבזים ביצירת חום, והדרישות לדריברים קטנים יותר מקטין יכולת פיזור אנרגיה ולא להפך, כך שאנו צריכים פטרון נוסף.

פיתרון שיטת PWM הינה בכיון הנכון, אומנם יש צורך בלדיק בתזמון על מנת שנוכל להגדיל את היעילות ולהגיע לכ- 98-99%.

לשם כך אנו צריכים למתג את טרזיסטורי ההספק בדיוק של ננו שניות, על מנת

שפעולה הBreak Before Make תתקים באופן מדוייק אבל מבלי לפגוע במעבר האנרגיה לעומס.

← אם להפעלה של טרנזיסטורי ההספק יש הפסקות רחבות, Break Before Make מובטח, אבל מעבר אנרגיה לעומס קטן.

← אם להפעלה של טרנזיסטורי ההספק יש הפסקות קצרות, מעבר האנרגיה לעומס רציף יותר אבל מסתכנים אי שמירה על Break Before Make תקין, משיכול לגרום לבזבוז אנרגיה רבה בפרקי זמן קצרים ולפגיע בטרנזיסטורי ההספק.

לכן נדרש מיתוג מדויק מעוד של טרזיסטורי ההספק. רווח נוסף הינו שמיתוג מדויק גם מאפשר עיצוב של זרמי המנוע רציפים יותר, משמקטין בנוסף את ערך הסלילים בפילטרים כך שגם פחות אנרגיה מתבזבז על התנגדות העצמית שלהם ושוב היעילות גודל.

על מנת למתג בדיוק כזאת גבוהה את הטרזיסטורים אנו משתמשים ברכיבי FPGA.

פיתוח החומרה של הדריבר ע”י FPGA מאפשר תיכנון תזמון מדוייק וחזרתי של סיגנל הבקרה.

מתוג מדויק מקל גם להעביר סטנדרטיים (רגולציות) :

- פחות חום, בטיחותי יותר ואמין יותר

- קל יותר לפלטר, פחות פליתת EMI

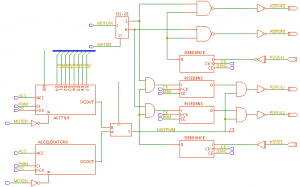

Example of a basic FPGA power driver (one phase shown)

Partial design of the FPGA schematics for the above driver

(note: the CAD used will output VHDL from the schematics)

2. יותר דיוק

דרישות הדיוק גם הם הולכים וגדלים.

שימוש באנקודרים, אקסלרומטרים, גירויים, מדי כח ולחץ בדיוקים גבוהים מצריכים גם הם להגיע לגבולות טכנולוגיות.

נפרת בהמשך בקיצור חלק מהאתגרים:

- במקרה של אנקודרים נדרשנו לפתח דריבר המסוגל לדייק במיקום פי 100 מהפולסים של האיקודר עצמו, לכן ממשנו שוב ע”י FPGA ׁׁׁ (אותו FPGA שבצידו השני דואג לדרייב נכון לטרזיסטורי ההספק) אלגוגוריטים שמאפשר חישוב פרדיקציה של המקום בין 2 פולסי האנקודר בדיוק טוב מ 1%.

התוצאה מדוייקת מכיוון ששינוי המהירות של העומס בין שתי פולסי האנקודר קטן יותר מ1% כך שאלוגוריטים הפרדיוקציה יכול לעדכן את החישוב בכל פולס אנקודר ולהיות מדוייק כפי שנדרש.

Design of the FPGA encoder prediction algorithm schematics for the above driver

(note: the CAD used will output VHDL from the schematics)

במקרה של סנסורים אנלוגיים בנינו קונדיטיונרים בדיוקים של 16bit עף על פי הקירבה הפיזית לאיזורי ייספק.

על מנת להגיע לדיוקים האלה סינכרנו את סיגנלי הADC לסיגנלי הדריב, גם זה מתאפשר מכיון שהגישה לADC ויצור כל סגנלי התזמון בשבילו מתבצע ע”י אותו FPGA שבצידו השני דואג לדרייב נכון לטרזיסטורי ההספק

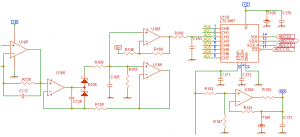

Partial design of a 16bit conditioner for the above driver

(only one sensor channel shown)

סיכום

בסופו של התהליך יש לנו דרייבר שכולל רק רכיב FPGA בגודל שיכול להיות גם3X3 מ”מ, טרזיסטורים באריזות גם מלימטריות על מעגל מודפס (שבעריכה נכונה) מסתדר עם מעט שכבות (רצוי רק 2).

דרייבר קטן ביותר המפעיל הספקים לא מבוטלים מבלי להתחמם ומבלי להקרין אנרגיה

אלקטרומגנטית לסביבה בדיוקים מדהימים.