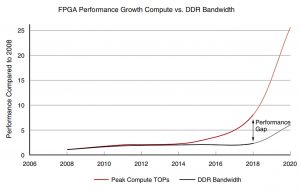

לרבים מבין עומסי העבודה והיישומים הקיימים בימינו, כגון אינטליגנציה מלאכותית (AI), ניתוח נתונים, המרת קידוד (transcoding) של וידיאו חי וניתוח גנום, יש צורך בכמות גדלה והולכת של רוחב פס. פתרונות מסורתיים של זיכרון DDR לא הצליחו עד כה לעמוד בדרישות המתרחבות האלו של מחשוב ורוחב פס, והם יוצרים צווארי בקבוק של נתונים. מצב זה נראה לעין באיור 1 אשר מציג את הגידול ביכולת המחשוב, בהשוואה לשיפור ברוחב הפס של זיכרונות DDR.

הגידול בביצועי מחשוב של התקני FPGA בהשוואה לרוחב פס של זיכרונות DDR

איור 1: השיפורים ביכולת המחשוב בהשוואה לרוחב הפס של זיכרונות DDR

זיכרונות עם רוחב פס גדול (HBM) יכולים להקל על צווארי בקבוק בצורה מוצלחת למדי, על ידי הוספה של קיבולת זיכרון ורוחב פס של נתונים. הפעולה נעשית על ידי שימוש בזיכרון מערכת במארז (SiP), טכנולוגיה המשמשת בזיכרונות על ידי הערמה (stacking) של שבבי זיכרון DRAM באופן אנכי ושימוש בממשק רחב (של 1024 סיביות).

למשל, התקני זיכרון מאופשרי רוחב פס גדול Virtex® UltraScale™ (VU+ HBM) מגשרים על פני הפער ברוחב הפס בעזרת יכולות משופרות ברוחב הפס עד 460 ג'יגה ביית בשנייה, אשר מסופק על ידי שני מערומי HBM2. התקנים אלו מכילים גם עד 2.85 מיליון תאים לוגיים ועד 9,024 פלחי (slice) DSP, שלהם יש יכולת אספקת שיא של 28.1 INT8 TOPs. בהתקני הזיכרון VU+ HBM, יש מתג AXI מוקשח שמאפשר גישה מכל אחד מבין 32 ערוצי AXI אל כל אחד מערוצי זיכרון HBM המדומים ואל זיכרון שניתן למיעון.

מאמר זה חוקר את היבטי התכנון שיכולים להשפיע לרעה על רוחב הפס של הזיכרון, את האפשרויות הקיימות לשיפור רוחב הפס, ולאחר מכן, את אחת הדרכים שבהן ניתן לאפיין את רוחב הפס של זיכרון HBM כדי לתאר את הפשרות. אפשר להשתמש באותן הטכניקות כדי לאפיין את רוחב הפס של זיכרון HBM בהתקני Alveo™ U280, Alveo™ VCU128 ובכל התקן זיכרון HBM מסוג UltraScale+™ של Xilinx. אפשר גם להשתמש בטכניקות אלו בכל יישום מואץ באמצעות ארכיטקטורת DSA קיימת או באמצעות ארכיטקטורות ייעודיות לתחום (DSA) מותאמות אישית. נסביר את התהליך ליצירת ארכיטקטורת DSA מותאמת אישית ב- Vivado® ואת דרך השימוש בפלטפורמת התוכנה Vitis™ המאוחדת של Xilinx כדי ליצור גרעינים (kernel) ותעבורת זיכרון ב- C/C++ על מנת לקבוע את הפרופיל של מחסניות זיכרון HBM.

מה יכול להשפיע על רוחב הפס של הזיכרון?

כל מי שעבד עם ממשקי זיכרונות DRAM חיצוניים יודע שהשגת רוחב הפס התיאורטי אינה אפשרית. למעשה, בתלות בכמה גורמים שונים, יכול להיות קשה אף להתקרב לכך.

תבנית התעבורה תורמת לרוחב פס גרוע. כתוצאה מכך לזיכרון DRAM נדרשות פעולות פתיחה (ACT) וסגירה (PRE) של שורות בתוך בנק זיכרון, ולפעולות גישה אקראית נדרשת תחזוקה רבה יותר, מצבים שבהם נמנעת העברה של נתונים. בנוסף, לחלק מהארכיטקטורות של זיכרון DRAM (כלומר DDR4 ו- HBM) יש תקורה הקשורה בפעולות גישה עוקבות לאותה קבוצת בנק זיכרון. והמשמעות של פרץ קצר של נתוני כתיבה/ קריאה או כאלה שמתבצעים לסירוגין היא, תנועה דו כיוונית של סיביות DQ וזמן סבב (turmaround) של אפיק שכרוך בכך, בזמן החלפת הכיוון.

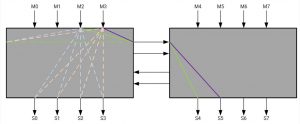

בזיכרון VU+ HBM, יש מתג AXI מוקשח אשר מאפשר גישה מכל אחד מבין 32 ערוצי AXI לכל אחד מבין ערוצי זיכרון HBM המדומים ולזיכרון הניתן למיעוון. קיימים יתרונות רבים לשימוש במתג מוקשח, כמו למשל מיעון גמיש, וכן, הפשטה של מורכבות התכנון והקטנה של גודש (congestion) הניתוב. על מנת לאפשר מיעון גמיש על פני כל ההיקף של מחסניות HBM, מכיל מתג AXI המוקשח תיבות מתגים שמחולקות לארבעה שולטים (master) X ארבעה נשלטים (slave).

איור 2: חיבורים פנימיים של מתג HBM

באופן כזה מתאפשר מיעון גמיש אבל יש מגבלה שעלולה להשפיע על רוחב הפס של הזיכרון. מאחר שקיימת אפשרות להשתמש רק בארבעה נתיבים אופקיים, מחסנית HBM יכולה להגביל את רוחב הפס האפשרי להשגה כתוצאה מפישור (arbitration).

כיצד אפשר להגדיל למקסימום את רוחב הפס של הזיכרון

כשמדובר בהגדלת רוחב הפס של הזיכרון למקסימום, יש לשקול שינוי בתבניות של הפקודות ושל המיעון. מאחר שגישה אקראית ופרצים (burst) קצרים של תנועות (transaction) קריאה/ כתיבה מניבים את רוחב הפס הגרוע ביותר, כדאי לבדוק אם יש אפשרות לשנות אותם ביישום המשתמש. כך תוכל לקבל את התמורה הגדולה ביותר על ההשקעה.

אם אינך יכול לשנות את תבנית התעבורה, ל- IP של בקר זיכרון HBM יש כמה אפשרויות שיכולות לעזור לך:

- Custom Address Mapping: כפי שצוין כבר, לאפשרויות גישה אקראית נדרשים קצבים גבוהים יותר של פקודות ACT ו- PRE. בעזרת מפת כתובות בהתאמה אישית, אפשר להגדיר כתובות AXI עבור כתובות של זיכרון HBM וכך, אף להגדיל את מספר בחירות הדף המוצלחות (page hit) ולשפר את רוחב הפס.

- Bank Group Interleave: מאפשר החלפה של פעולה במיעון סדרתי בין קבוצות בנק (זיכרון) זוגיות ואי זוגיות, על מנת להגדיל למקסימום את יעילות רוחב הפס.

- Enable Request Re–Ordering: מאפשר לבקר לסדר מחדש פקודות (כלומר למזג פקודות כדי לקצר את זמני המחזור של האפיק).

- Enable Close Page Reorder: מאפשר לבקר לסגור דף לאחר שפקודה הושלמה. אם סגירה זו אינה מאופשרת, הדף יישאר פתוח, עד אשר פעולה בעדיפות גבוהה יותר תתבקש עבור דף אחר באותו בנק. לאפשרות זו יכול להיות יתרון, אם ייעשה שימוש בתבנית מיעון אקראית, ליניארית או בהתאמה אישית.

- Enable Look Ahead Pre–Charge: מאפשר לבקר לסדר מחדש פקודות על מנת להקטין למינימום פקודות PRE.

- Enable Look Ahead Activate: מאפשר לבקר לסדר מחדש פקודות על מנת להקטין למינימום פקודות ACT.

- Enable Look Ahead Single Bank Refresh: מאפשר לבקר להוסיף פעולות רענון בהתבסס על פעולות שממתינות לביצוע על מנת להגדיל את היעילות למקסימום.

- Single Bank Refresh: מעביר לבקר הוראה לרענן בנקים, כל אחד בנפרד, במקום את כולם ביחד.

- Enable Refresh Period Temperature Compensation: פקודה זו מאפשרת לבקר לכוונן באופן דינמי את קצב הרענון בהתבסס על הטמפרטורה של מחסניות הזיכרון.

- Hold Off Refresh for Read/Write: פקודה זו מאפשרת לבקר להשהות פעולת רענון כדי לאפשר את השלמת הפעולות קודם לכן.

ניטור זיכרון HBM

ניטור זיכרון HBM הוא חידוש של Vivado אשר בדומה ל- SysMon יכול להציג את טמפרטורת השבב באופן נפרד לכל מחסנית שבב HBM2. הוא יכול גם להציג את רוחב הפס על בסיס של כל MC או ערוץ מדומה (PC).

על מנת לקבוע בצורה נכונה את הפרופיל של תכנון החומרה ואת התצורה של זיכרון HBM יש להתחיל בהגדרות HBM של ברירת המחדל וללכוד את תפוקות הקריאה/ כתיבה כדי שישמשו כנקודת הבסיס. לאחר מכן יש ליצור מחדש קובצי .bit חדשים באמצעות כל אחד מהצירופים של אפשרויות HBM MC שנידונו קודם כדי לקבוע איזה מביניהם מספק את התפוקה הגבוהה ביותר. יש לשים לב שהאופן שבו מוגדרת הקונפיגורציה של מתג AXI Switch יכול אף הוא להשפיע על רוחב הפס של זיכרון HBM ועל התפוקה שלו ויש לשקול לקבוע גם את הפרופיל שלו.

אם משתמשים בתכנון קיים ובכלי Vitis, יש צורך לשנות את פלטפורמת החומרה באמצעות זרימת DSA בהתאמה אישית.

דרישות תכנון

על מנת לקבוע את הפרופיל של רוחב הפס של זיכרון HBM יש ליצור תכנון או יישום או להשתמש בתכנון או יישום קיימים. על מנת לקבוע את הפרופיל של קונפיגורציות HBM אחרות יש צורך לגשת לתכנון החומרה ולשנות את ליבת HBM IP ולאחר מכן, ליצור זרימות חדשות של סיביות ו/ או קובצי .xsa/ .dsa אשר משמשים בכלי Vitis לצורך פיתוח תוכנה.

כרקע, Vitis הוא כלי תוכנה מאוחד שפותח על ידי חברת Xilinix ומספק מסגרת לפיתוח ולאספקה של יישומים למרכזי נתונים הפועלים בהאצת FPGA ומשתמשים בשפות תכנות סטנדרטיות וליצירת פלטפורמות תוכנה שמיועדות למעבדים משובצים.

לקבלת תכנונים קיימים יש לעיין ב- Github, במאגרי מידע SDAccel לדוגמה, בדף המוצר U280 ובדף המוצר VCU128 אשר מכיל תכנוני ייחוס מוכוונים (TRD). אפשר להשתמש בפלטפורמה בהתאמה אישית, או אף ב- U280 או ב- VCU128 ואפשר גם ליצור תכנון מותאם אישית של פלטפורמת חומרה.

נשאלת השאלה, למה עלינו ליצור פלטפורמת חומרה בהתאמה אישית עבור Alveo U280, אם קיימות כבר ארכיטקטורות DSA? עם התפתחותם של אלגוריתמים לעומסי עבודה, חומרה שניתנת לקונפיגורציה מאפשרת ל- Alveo להתאים את עצמה מהר יותר ממשך הזמן של מחזורי פיתוח מוצר של כרטיסים קשיחים של מאיצי פונקציות. הגמישות בתהליך ההתאמה האישית ובקביעת הקונפיגורציה של החומרה, מעניקה ל- Alveo יתרונות ייחודיים לעומת המתחרים. בהקשר של מאמר הדרכה זה, היינו מבקשים להתאים באופן אישי פלטפורמות חומרה חדשות וליצור אותן תוך שימוש בקונפיגורציות שונות של ליבת HBM IP על מנת ליצור פרופיל של ההשפעות הקיימות על רוחב הפס של הזיכרון, כדי שנוכל לקבוע איזו פלטפורמה מספקת את התוצאות הטובות ביותר.

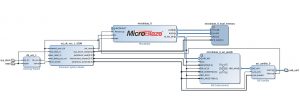

פלטפורמת חומרה בהתאמה אישית אפשר ליצור בכמה דרכים, אבל המהירה מכולן היא באמצעות שימוש במחולל Vivado IP Generator (IPI). בהמשך מתוארת כדוגמה, אחת הדרכים, שמשתמשת Microblaze כדי ליצור תעבורת זיכרון HBM בתוכנה. אפשר גם להגיע לאותה תוצאה דרך שימוש ב- HLS, ב- SDAccel או בכלי Vitis עם תעבורת זיכרון מואצת בחומרה. השימוש ב- Microblaze כבמחולל התעבורה מקל את הבקרה של תבנית התעבורה לרבות מיקומי כתובות. אפשר להשתמש בתבנית בדיקת זיכרון של ברירת המחדל, כדי ליצור לולאות ותבניות שונות ולשנות אותן, שיעזרו לקבוע בצורה יעילה את פרופיל רוחב הפס של זיכרון HBM.

הצעדים של בניית תכנון בכלי Vitis או בערכת SDK דומים, ויכללו פעולות כגון אלו המתוארות בהמשך:

- פתיחת Vivado

File => Projec => New (קובץ => פרויקט => חדש)

- יצירה של תכנון Vivado חדש או פתיחת תכנון קיים

- הכוונה אל U280, VCU128 או אל כל התקן US+ EBM שנמצא בשימוש

- יצירת תכנון בלוקים

- הוספת ליבת HBM IP

הערה: יש לוודא שהפרוייקט מכיל תכנון בלוקי IP Integrator (IPI) אשר כולל זיכרון HBM

ו-Microblaze. אנו מתייחסים לתכנון בלוקים זה כתכנון החומרה. על מנת להשיג רוחב פס שיהיה כמעט רוחב הפס התיאורטי המרבי (460 ג'יגה ביית בשנייה) עבור שתי מחסניות HBM2, יש צורך לדחוף תעבורה רציפה אל כל 16 בקרי הזיכרון (MC) הזמינים דרך ערוצי AXI.

יש להוסיף MicroBlaze, מקמ"ש UART וכל IP היקפי נוסף שנדרש.

איור 3: דוגמה של תכנון בלוקים של זיכרון HBM.

- תיקוף התכנון ויצירה של מוצרי המוצא

- validate_bd_design

- generate_target all [get_files <>.bd]

- יצירת כלי עיטוף ל- HDL (HDL wrapper) עבור .bd

- make_wrapper- files [get_files <>.bd]

- הפעלת סינתזה

- הפעלת מימוש

- יצירת Bitstream (זרם סיביות)

- ייצוא חומרה

- File=>Export Hardware

- בשימוש עם הכלי Vitis ייתכן שיהיה צור לעקוב אחר ההוראות הבאות

- (בשימוש בגרסה 2019.2) write_hw_platform –fixed <>/xsa

- (בשימוש בגרסה 2019.1) write_dsa –fixed <>.dsa

- הפעל את הכלי Vitis

- בחר מרחב עבודה

- יצירה של פרוייקט יישומי חדש וחבילת תמיכה במעגל (Board Support Package)

- יש ללחוץ Next, לבחור Create from hardware, ללחוץ "+" ולהצביע על .xsa

- יש ללחוץ Next, לבחור CPU Microblaze, Language C

- יש ללחוץ Next, לבחור "Memory Tests" וללחוץ Finish

- יש לבנות ולהפעיל בדיקת זיכרון במטרה

איור 4: יצירת פרוייקט יישומי חדש

מסקנות

מאמר זה מסביר מדוע על מנת לעמוד בדרישות רוחב הפס המתרחב של זיכרון DDR יש צורך בזיכרון HBM, מה אפשר לעשות כדי להשפיע על רוחב הפס של זיכרון DRAM, מהן האפשרויות הקיימות להגדלה של רוחב הפס עד למקסימום וכיצד לנטר וליצור פרופיל של התוצאות.

השימוש בטכנולוגיית Vitis על מנת ליצור תעבורת זיכרון HBM ולהאיץ אותה, הוא דרך מהירה וקלה שבה ניתן לאמת את דרישות רוחב הפס ולוודא ציות לדרישות אלו, תוך כדי יצירת פרופילים של קונפיגורציות זיכרון HBM שונות, כדי לקבוע איזו תהיה אופטימלית עבור המערכת.