סקירה כללית

כדי להבטיח בטיחות ואבטחה פונקציונליים בתכנונים, למשל תכנונים המשמשים ביישומים תעשייתיים, יישומים רפואיים, תעשיות הרכב, חלל ויישומים צבאיים, יש צורך ביותר מאשר אימות פונקציונלי מסורתי (סימולציות וכו'). גם אם נאתר ונתקן כל אחת מהשגיאות, נדרש הרבה יותר מיישומים אלו כדי להיות בעלי אמינות פונקציונלית גבוהה ביותר. הם צריכים להיות בעלי יכולת לטפל במגוון של תקלות ושגיאות שנגזרות, בין אם על ידי תיקון אוטומטי של השגיאות או על ידי גילוי שלהם ונקיטת פעולות כגון כיבוי מנגנון או איפוס באופן בטוח מבחינה פונקציונלית . תקלות יכולות להתרחש על ידי הפרעות מחלקיקי קרינה (radiation particle upset), או מתופעות של חימום, אספקת מתח וגורמים סביבתיים אחרים. רכיבי FPGA הם בחירה נפוצה בתכנונים אלו , בזכות הגמישות המובנית שלהם לאמינות גבוהה ובזכות העלויות הנמוכות שלהם, בהשוואה למעגלי ASIC כשמדובר ביישומים בכמויות קטנות.

תכנונים של מערכות קריטיות לבטיחות

יישומי חלל ויישומים צבאיים או רפואיים וכן יישומים הקשורים לרכבים ועוד הם דוגמאות ליישומים שדורשים בטיחות פונקציונלית ואמינות גבוהה באופן יוצא דופן. אסור לסכן את הפעולה התקינה באחד מהיישומים האלה, שעלולה להתרחש למשל, אם מסיבה כלשהיא (קרינה, חום,תקלות מתח ועוד) סיבית אחת תשנה מצב באופן אקראי במכונות מצבים או בכתיבה לזיכרונות בתיכנון הממומש ב- FPGA מה שיוכל לגרום למשל בישומי חלל, לשיבוש בתקשורת מול הלווין ואף לתקלות חמורות מאלו שעלולות להוריד לטמיון את כל ההשקעה בפרוייקט ולכן חייבת להיות בתיכנון יכולת לזהות ולתקן שגיאות מעין אלו תוך כדי פעולת תיקון אוטומטית או לחילופין להשתקם מהשגיאה באמצעות איפוס (reset) של המערכת לאחר מעבר למצב בטוח.

גם דרישות הבטיחות מיישומים רפואיים ברורות מאוד. מכשירים שבאמצעותם מתבצעים טיפולים בקרינה, דימות בקרני X (קרני רנטגן), בתהודה מגנטית (MRI) וסריקת אולטרה סאונד חייבים לפעול בגבולות בטוחים.

רבים מבין היישומים התעשייתיים, לרבות רובוטים, עלולים לגרום לפציעה או למוות אם תהיה בהם תקלה שתגרום להם לפעול באופן לא בטוח.

קיימים כמה מקורות לתקלות בשבבים, לרבות טמפרטורה, תהליך, אספקת מתח, קרינה ותקלה ברכיב. תקלות אלו עלולות להוביל לתקלות קבועות. סוגים אחרים של תקלות, כגון תקלות שיבוש אות (glitch) או היפוך סיבית (bit flip) הן תקלות חולפות, ולעתים, אפשר לאפס אותן על ידי פעולה ברמת המערכת.

קרינה ויינון הם מקורות בעלי חשיבות לתקלות מעבר, במיוחד ביישומים מבוססי מקום. ההשפעה של יינון או של קרינה על השבב באה לידי ביטוי בשיבוש חולף של אות. הוא מסווג כתופעת מעבר של אירוע יחיד (SET -SINGLE EVENT TRANSIENT ) מאחר שהוא מתרחש באופן חד פעמי, ולאחר מכן האות מתייצב. אם האות החד (spike) מופיע קרוב לדגימת אות השעון, יש אפשרות שתקלת השיבוש תיקלט על ידי המודול הדוגם (sequential element). התוצאה תהיה ערך שגוי, ושגיאה זו עלולה לעבור הלאה ולגרום לפעולה לא תקינה או אף לתקלה מערכתית.

תכנון לבטיחות

אנשי תכנון פיתחו טווח רחב של טכניקות שמאפשרות לעמוד בתקלות על ידי הכללה של מנגנוני בטיחות פונקציונליים בתכנון של שבב. אחת הדוגמאות היא הוספת סיביות של קוד תיקון שגיאות (ECC) לזיכרונות או לאוגרים. יתירות (redundancy) חלקית של הנתונים השמורים יכולה לתקן סיביות שהתהפכו כתוצאה מתקלות או לזהות אותן.

אם תקלת שיבוש מועברת אל אוגר המצבים של מכונת מצבים סופיים (FSM), מכונת המצבים הסופיים עלולה לעבור למצב לא מוגדר או לקיפאון (deadlock), שיגרמו לתקלת מערכת. קיימות כמה טכניקות תכנון בטוחות שמאפשרות להפוך מכונת FSM לעמידה בפני תקלות מסוג זה, על ידי מניעה של נעילה והשתקמות כאשר מזוהה מצב לא חוקי.

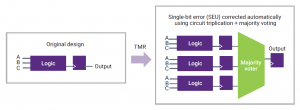

אפשר לזהות תקלות של נתיב הנתונים ושל הבקרה ולטפל בהן בעזרת יתירות משולשת של המודול (TMR – TRIPLE MODULE REDUNDANCY ).

האיור הבא מתאר יתירות מסוג TMR. הלוגיקה הקריטית לבטיחות מוכפלת פי שלושה וכל אחד מהמוצאים של כל שלושת המודולים (בלוקים) מוזן אל יחידת בחירת הרוב (majority voter). אם הפרעה של אירוע יחיד (SEU) מתרחשת באחד משלושת המודולים ומייצרת ערך שגוי במוצא, יחידת בחירת הרוב תבחר בערך הנכון מתוך שני העותקים הנותרים של המודול. באופן כזה, תקלות יחידות ממוסכות ואין השפעה לתקלה על הפונקציונליות של התכנון. .

איור 1: יתירות משולשת של מודול ממסכת תקלות בדידות

אוטומציה של תכנון לקבלת תכנונים בעלי אמינות גבוהה

לכל צורות התכנון לבטיחות פונקציונלית נדרש מאמץ משמעותי אם מוסיפים באופן ידני מנגנוני בטיחות לתכנון ברמת העברת האוגרים (RTL). יתירות TMR יכולה להיראות עניין פשוט של העתק–הדבק (פעמיים), אך בכל פעם, כאשר מתבצעים שינויים כדי לתקן שגיאות או כדי לשפר תזמונים, יש לבצע את פעולות העריכה ברמת לוגיקת RTL בכל שלושת העותקים, וכן להתמודד עם סימולציות ברמות השונות של התיכנון (RTRL, Synthesis, P&R, Debug) בכדי לוודא מעבר בטוח בין המצבים השונים וכן אפשרות לא רק לתקן את הבעיה בזמן אמת אלא גם לדווח עליה.התכנון לבטיחות הופך להיות יעיל ועמיד יותר בהרבה, כאשר הוא מתבצע באופן אוטומטי.

שלב הסינטיזה הוא השלב הטוב ביותר להוספה אוטומטית של מנגנוני בטיחות מעין אלו . כלי הסינטיזה SYNPLIFY של חברת SYNOPSYS ל-FPGA הוא הסביבה המתקדמת ביותר בתעשייה לתכנון ולניפוי שגיאות בתכנון התקני FPGA, וכולל אפשרות לסמלץ את מגוון השגיאות האפשריות וכן לבדוק (Debug) בזמן אמת בעיות שיכולות לשבש את הפעולה התיקנית של המעגל ברכיבי FPGA.

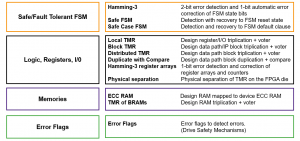

כלי ה- SYNPLIFY תומך בטכניקות נפוצות רבות של תכנון לבטיחות. באלו נכללות גילוי שגיאות, תיקון שגיאות, שיקום משגיאות וכמה גרסאות של יתירות TMR ברמות מתקדמות.

כל מנגנוני הבטיחות שנוספו על ידי SYNPLIFY מיושמים עם מאפיינים של המשתמש, ולכן אין צורך בשינויים ברמת RTL של התכנון (המאפיינים מוכנסים לכלי דרך קובץ חיצוני !). כך מתאפשר מימוש מהיר של תכנוני RTL מוכחים ומאומתים. איור 2 מתאר את מנגנוני האמינות הגבוהה שנתמכים על ידי SYNPLIFY . אפשר להחיל במהירות את היכולות הנרחבות האלו דרך מאפיינים, על מנת לממש אותם סעיפים של התכנון, שהם קריטיים לבטיחות באמינות גבוהה. אפשר גם לממש דגלי שגיאות כדי לנטר שגיאות שמתגלות ולהניע מנגנונים של בטיחות.

איור 2. מנגנוני אוטומציה באמינות גבוהה

אימות תכנון לקבלת תכנונים בעלי אמינות גבוהה

לאחר המימוש של מנגנוני בטיחות בתכנון, יש לאמת אותם. סיכום הכלים הקיימים, שהם ייחודיים לאימות באמינות גבוהה, מפורט בהמשך.

SYNPLIFY– איתור שגיאות בזמן אמת

יכולת צפייה פנימה (Observability) אל כל צומתי התכנון ודגלי השגיאות מתקבלת בביצועי זמן אמת עם נתונים אמיתיים שפועלים "במצב חי" במערכי FPGA. המשתמשים יכולים להחדיר שגיאות שרירותיות בזמן אמת ולנטר את הנתונים האמיתיים, כדי לקבוע את היעילות של המנגנונים או לנטר אותות קריטיים במהלך בדיקות המערכת.

Z01X של Synopsys – הדמיית שגיאות

הדמיית השגיאות Z01X™ של Synopsys מוסיפה באופן אוטומטי תקלות "פינים תקועים" (stuck-at) ותופעות מעבר ומדמה אותן. יש לה ביצועים ויכולת לטפל במספר רב של שגיאות אפשריות בהתקני FPGA המורכבים ביותר. היא משתמשת באלגוריתם להדמיה של תקלות בו זמניות אשר מזריק תקלות מרובות בו זמנית. דוחות מקיפים מופקים לגבי ההשפעות של התקלות שהוזרקו בסביבת ההדמיה והאם הם התגלו ותוקנו ע"י מנגנוני שיכוך השגיאות .

סיכום

ביישומים רבים קיימת דרישה לתכנונים של מערכי FPGA קריטיים לבטיחות. SYNPLIFY מוסיפה באופן אוטומטי את מנגנוני הבטיחות הדרושים, כדי להגן מפני תקלות ממקור פנימי וחיצוני. Z01X מספקת יכולות מובילות בתעשייה של הזרקת שגיאות והדמיית תקלות, כדי לאפשר אימות של מנגנוני הבטיחות ולחשב את הסטטיסטיקה של כיסוי התקלות הנדרשת על ידי תקני הבטיחות. מבחינת הביצועים, יכולת השימוש וקלות השימוש, זרימת הבטיחות הפונקציונלית של Synopsys היא חסרת תקדים ומהווה פריצת דרך אמיתית בתחום חשוב זה .