מאת: Henning Nicolaisen, Tor Holmboe, Karina Vieira Hoel,

מאת: Henning Nicolaisen, Tor Holmboe, Karina Vieira Hoel,

Stein Kristoffersen, University of Oslo

פותח מיתקן המחשה למכ”ם דופלר-טווח (range-Doppler) בתחום X בעל רזולוציה גבוהה, מבוסס על כרטיס מסחרי של עיבוד אותות דיגיטלי בגודל 6U-VXS, המכיל את כל מעגלי תחום-הבסיס הדרושים. התכנון המיוחד מכיל ממיר מעלה ומוריד תדרי רדיו, קושחת FPGA ותוכנת PC. רוחב-פס האותות המעשי הוא קרוב ל-1 גיגה-הרץ ורזולוציית התחום היא קרובה ל-15 סמ’. הפונקציונליות הוכחה בניסוי קרינה בחלל חופשי.

כאשר קיימת מגבלה של מקום או משקל, רצוי ביותר לבחור בפלטפורמת חומרה מוכללת יחידה שיכולה למתג בין מגוון רחב של משימות או תפקידים, לרוב בגין עיצוב מחדש של התוכנה והקושחה.

באופן מסורתי, מערכות בתדר רדיו (RF) מבוססות על חומרה מיוחדת, כגון מעגלי ASIC. חומרה כזו מציעה עיצוב חוזר מוגבל או אפסי, והיכולת להשתמש שוב במערכת עבור יישומים אחרים היא מוגבלת. הפיתוח השוטף של מודולי חומרה מסחריים

(commercial-off-the-shelf-COTS) מוכללים עתיד לשנות מצב זה. מודולים המכילים ממירי אנלוגי לדיגיטלי (ADC) ודיגיטלי לאנלוגי (DAC) ביחד עם משאבי עיבוד אותות דיגיטלי נרחבים, במיוחד field programmable gate arrays – FPGA, מקלים על מימוש מערכות מרובות-מטלות כגון אלה. ניתן לעצב מחדש FPGA תוך שניות, דבר המאפשר מיתוג מהיר בין הפונקציות השונות.

מאמר זה מתאר את מימוש אחד המודולים הללו, כרטיס ה-[TRITON VXS-1 [1, במיתקן המחשה של טכנולוגיית RF רבת-משימות מתוכננת המכונה MuPuRF. מערכת ה-MuPuRF נועדה להציג יכולות במכ”ם ובלוחמה אלקטרונית (EW), כלומר תקיפה אלקטרונית (electronic attack – EA) ותמיכה אלקטרונית (electronic support – ES).

הגרסה הראשונה של מערכת המכ”ם מומשה לאחרונה והיא מוצגת להלן. את הגרסאות הנוספות של ה-MuPuRF יש עדיין לממש.

רזולוציית המכ”ם בטווח ובדופלר ניתנת לשינוי בתוך גבולות נרחבים, מהרזולוציה האופיינית למכ”מי דופלר-טווח למטרות אוויר עד הרזולוציה הגבוהה הנדרשת במערכות מכ”ם בעל מפתח סינתטי (synthetic aperture radars – SAR) ו-(inverse SAR (ISAR. אולם, לא מומשו פונקציית קיזוז על מסלול המכ”ם, היגוי האנטנה או מעקב אחר מטרות, ומוד המכ”ם MuPuRF איננו מייצג מערכת תפעולית במובן זה. רוחב הפס Nyquist של האות הדיגיטלי של ה-MuPuRF הוא 1 גיגה-הרץ, התואם רזולוציה של טווח תיאורטי של 15 סמ’.

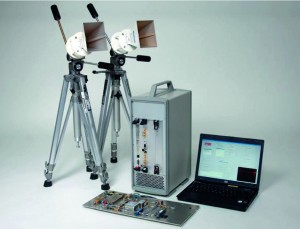

איור 1 מראה את היחידות השונות של מערכת ה-MuPuRF. ה-TRITON מורכב בתיבת VXS בעלת 5 חריצים. התפקיד היחידי של המישור האחורי הוא לספק הספק. יחידת הממיר מעלה-מוריד RF מוצגת בצורתה הראשונית, המורכבת על לוח אלומיניום בקדמת התמונה. המגבר נמוך הרעש (low-noise amplifier – LNA) של המקלט (Rx), מגבר ההספק power של המשדר (Tx) והחיווט אינם מתוארים.

כרטיס TRITON VXS-1

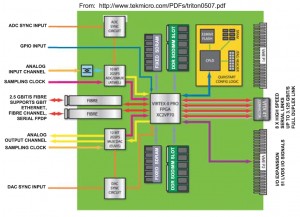

ה-TRITON VXS-1, המיוצר על-ידי [Tekmicro [2, הוא כרטיס U6 חד-חריץ בעל גורם צורה (form factor) והוא תואם את המפרט VITA 41.0 VXS. יישומי-המפתח הנפוצים של ה- TRITON VXS-1 כוללים מכ”ם, לוחמה אלקטרונית, תוכנת רדיו ותקשורת. איור 2 מראה את המרכיבים הראשיים ונתיבי האותות שלו. ליבת ה-TRITON VXS-1 היא מעגל FPGA Xilinx Virtex-II Pro ביחד עם ADC של

10 – ביט ו-DAC של 12 – ביט. שני הממירים יכולים לפעול בקצב של 2 Gsamples/sec, המקנה רוחב-פס דיגיטלי Nyquist של 1 גיגה-הרץ. רוחב-הפס האנלוגי ב-3dB הוא מ-3 מגה-הרץ ל-3 גיגה-הרץ.

תקן ה-VXS ירש את המחברים 1P ו-2P מתקן VME 64, אך הם משמשים להזנת הכרטיס בלבד. הממשק VME bus בעצמו איננו מיושם מלבד עבור 51 אותות מוגדרים על-ידי המשתמש במחבר 2P. ה-IO לבקרה ונתונים מהירים עבור הכרטיס מיושם בעיקר תוך שימוש בקשרים הטוריים המהירים המצויים בפנל הקדמי (לדוגמה Ethernet Gigabit) ו/או מחבר הלוח האחורי 0P VXS, הממוקם בין 1P ו-2P.

הכרטיס כולל שני מאגרים של זיכרון 0.5 Gbyte SDRAM DDR קבוע ושני שקעים של מודולי SODIMM DDR התואמים מודולים עד 2 Gbyte, המקנים נפח זיכרון מרבי של 5 Gbyte. אולם המערכת המצויה כרגע היא בעלת נפח זיכרון כולל של 2 Gbyte. הזיכרון הפנימי של ה-FPGA מתווסף לכך.

את ה-FPGA ניתן לעצב בשלושה אופנים: מזיכרון הבזק על הכרטיס במהלך ההזנה, דרך מחבר ה-JTAG על הכרטיס או דרך ה- Gigabit Ethernet על הפנל הקדמי.

ניתן להשיג ערכת פיתוח המכילה ספריות של ליבות קנייניות של FPGA ותוכנת PC. הערכה כוללת גם קוד מקור FPGA ו-PC עבור שני תכנוני ייחוס. הראשון הוא מערכת משולבת של ליכוד נתוני-בזק (snapshot) והפקת צורות-גל אקראיות, והשני הוא מערכת loop-around המריצה את נתוני ה-ADC ישירות אל ה-DAC. סביבת התכנון הרצויה היא Xilinx ISE ו-Microsoft Visual Studio.

תכנון ופונקציונליות של המכ”ם MuPuRF

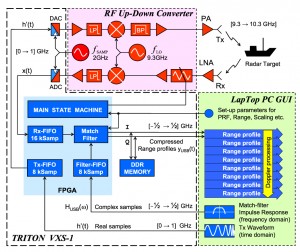

איור 3 מציג דיאגרמת בלוקים פונקציונלית של מערכת המכ”ם MuPuRF. היא מורכבת משלושה יחידות עיקריות, ממיר התדר RF העולה/יורד, ה-TRITON ומחשב נייד המריץ את הממשק הגרפי של המשתמש (graphical user interface – GUI). מתוארים גם LNA של ה-Rx ו-PA של ה-Tx. המכ”ם משתמש בשתי אנטנות Rx ו-Tx נפרדות, והוא מסוגל לבצע פעולה בו-זמנית של ה-Tx וה-Rx.

משתמשים בהמרת RF עולה/יורדת חד-ערוצית וחד-שלבית. ממיר עולה/יורד מורכב יותר עשוי להידרש כדי לאפשר פעולה רב-משימתית, אך התכנון הנוכחי עונה להפעלה מעבדתית מוגבלת ב-תחום X. הרגישות במחבר מבוא ה-RF היא כזו שרמת מבוא של -45 dBm מתאימה לתחום הסקלה המלאה של הADC-10- ביט. כל שבח LNA מתווסף לכך. מנחת מיתכנת מהיר בעל תחום של 60 dB יכול לשמש כדי לפצות עבור התלות 1/R4 בתחום וכדי לבצע התאמות רגישות כלליות תחת בקרת התוכנה.

ה-FPGA משמש בעיקר עבור פונקציות קריטיות-לזמן הכוללות שידור צורת-הגל של פולס ה-Tx אל ה-DAC בתדר חזרה (pulse repetition frequency- PRF) קבוע, וכדי לרשום את ההדים התואמים ממרווח הטווח או התרחיש הנכונים. פונקציות בקרה אלו ממומשות במכונת המצבים הראשית. פרמטרי כוונון כגון אורך הפולס, תחילה וסיום התרחיש, מרווח חזרת הפולס (pulse repetition interval – PRI) ומספר הפולסים במרווח עיבוד הדופלר נבחרים ב-GUI ה-PC ומועברים ל-TRITON. ניתן לתכנת עד ארבעה PRIs שונים עבור פרצי פולס עוקבים אוטומטיים כדי למנוע דו-משמעויות בטווח או בדופלר.

המכ”ם יכול לפעול תוך שימוש בכל צורת-גל בתוך רוחב-הפס המרבי של 1 גיגה-הרץ. צורת-הגל הרצויה נבחרת ומופקת ב-GUI של ה-PC ומועברת ל-TRITON ביחד עם יתר פרמטרי המכ”ם. אורך הפולס מוגבל כיום לגודל הזיכרון של ה-Tx-FIFO שהוא 8 kSamples בתצורה הנוכחית. עם צורת-גל בעלת רוחב-פס מלא (כלומר 2 G Samples/s) הדבר שווה-ערך לפולס של 4 מיקרו-שניות.

אות ה-Rx הדיגיטלי בפס-בסיס נשמר בזיכרון ה-Rx-FIFO עם קבלתו. גודל חוצץ (buffer) זה הוא 16 kSamples המתאים למרווח טווח דגימה מרבי של 1229 מ’ במקרה של צורת-גל ברוחב-פס מלא של 1 גיגה-הרץ.

במקרה שלצורת-הגל יש החלק ה-1/N מרוחב-הפס המלא, מהירות הדגימה היעילה ניתנת להפחתה בהתאם באמצעות דגימה חוזרת של זרמי הנתונים של ה-DAC וה-ADC באופן פנימי ב-FPGA. דבר זה יעלה את אורך הפולס המרבי, גודל תא הטווח ואורך התרחיש המרבי בגורם N, תוך שמירה על מהירות העיבוד.

מסנן מתואם (match filter) משולב בזמן-אמת ומפענח ניצב ממומש ב-FPGA. היענות המסנן הרצויה מועברת מה-PC אל ה-FIFO-מסנן של ה-FPGA. מימוש המפענח-מסנן המשולב מתואר בפרק IV. השהיית התהליך של המסנן-מפענח תלויה במספר דגימות ה-Rx, והיא הגורם המגביל של ה-PRF המרבי שניתן להשיג בפעולה בזמן אמת. במקרה של PRFs גבוהים יותר, יש לבטל את והמסנן-מפענח, והפעולה תבוצע במקומו במהירות הרבה יותר נמוכה ב-PC. המוצא של המסנן-מפענח FPGA, כלומר פרופילי הטווח הנדחסים, מועבר ל-RAM DDR של ה-TRITON ולאחר מכן ל-PC לשם עיבוד דופלר, תצוגה ואחסון הנתונים.

כל אותות העברת הנתונים, התצורה והבקרה בין ה-TRITON וה-PC מתנהלים דרך Gigabit Ethernet.

תכנון ה-FPGA מפותח בסביבת ה-Xilinx ISE, תוך שימוש בליבות ה-IP של מפתחי ה-TRITON לשם ממשק אל ה-ADC, DAC, DDR, RAM ו-Gigabit Ethernet.

ה-GUI, כולל העיבוד והפונקציות הכלולות, מפותח ב-Visual Studio ופועל במחשב הנישא עם מערכת הפעלה של חלונות XP.

מסנן מתואם ומפענח ניצב

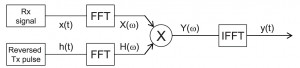

האות תחום-בסיס Tx המסומן (h’(t נבחר ומופק ב-GUI ה-PC כסדרת-זמן של 2 Gs/s המורכבת מדגימות ממשיות. היענות לפולסים במישור הזמן (h(t של המסנן המתואם הליניארי המיטבי שווה לגרסה הפוכת-הזמן של הפולס המשודר (h’(t . המוצא (y(t של מסנן מתואם ליניארי כזה הוא העווית (convolution) של היענות הפולס (h(t עם ההד הנקלט (x(t. יתרה מזו, ספקטרום (Fourier Y(ω שלה שווה למכפלה המרוכבת של הספקטרומים (H(ω ו-(X(ω. ב-MuPuRF היחס האחרון משמש כאשר תאום המסנן מבוצע במישור התדר דרך השימוש ב-(Fast Fourier Transform (FFT וה-FFT ההפוך כמתואר באיור 4. סדרת הזמן (h(t מורחבת אל האפס כדי של-(H(ωתהיה אותה הרזולוציה כמו ל-(X(ω.

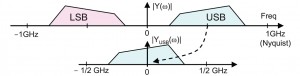

יתר על כן, מוצא המסנן המתואם (y(t, כלומר פרופיל הטווח הדחוס, חייב להיות מפוענח בניצב לרכיבי במופע וניצבים I&Q כדי שעיבוד הדופלר הבא יאפשר הבחנה בין הזזות דופלר חיוביות ושליליות. מאחר שהאות המשודר מורכב מדגימות ממשיות בלבד, כך יהיה גם ההד הדחוס (y(t. ספקטרום Fourier של (y(t הוא לכן סימטרי מסביב לאפס, והוא מורכב מפס-צד עליון (upper sideband – USB) ותחתון (lower -LSB) בעלי תוכן זהה, כמתואר בחלק באיור 5. הפענוח הניצב מבוצע במישור התדר על-ידי הזזה כלפי מטה של ה-USB של הספקטרום בכמות מחצית תדר Nyquist, ובאותו הזמן בהרחקה של פס הצד התחתון (LSB). תהליך זה מתואר כמעבר מ-(Y(ω ל-(YUSB(ω באיור 5. מאחר ש-(YUSB(ω איננו סימטרי מסביב ל-0 הרץ, סדרת הזמן (yUSB(t המתאימה היא מרוכבת, כלומר כוללת מרכיבי I ו-Q. מספר הדגימות הדיסקרטיות ב-(YUSB(ωהוא מחצית המספר ב-(Y(ω ומספר הדגימות ב-(yUSB(t הוא מחצית המספר ב-(y(t. קצב הדגימה של (yUSB(t הוא לכן 1 גיגה-הרץ. בשל סיבות מחשוב, הפענוח הניצב נדחף לאחור והוא משמש בפונקציית המעבר (H(ω של המסנן המתואם וההד הנקלט X(ω) ולא ישירות ב-(Y(ω, כמתואר באיור 6.

ה-FFT וה-IFFT הממומש הוא Coregen IP של Xilinx, כאשר ל-[FFT v5.0 [4 יש ארכיטקטורת radix-4 ואריתמטיקה ללא קנה-מידה, בעלת נקודה קבועה. ל-FFT רוחב מבוא שנקבע ל- (10+10) ביט והמוצא (25+25) ביט. המבוא מה-ADC הוא ממשי ולכן המרכיב המדומה של המבוא מכוון לאפס. רוחב המבוא של ה-IFFT נקבע ל-(16+16) ביט והמוצא ל-(30+30) ביט.

הרכיבים Scale A ו-Scale B, המוצגים באיור 6, הם גדלים סקלריים חצי-קבועים. הסקלרים מתוכנתים על-ידי ה-GUI של ה-PC כמבוסס על עצמת האות החזויה או הנמדדת. גישה חלופית היא להשתמש ב- FFT בקנה מידה או בעל נקודה קבועה. אולם רכיבים אלה משתמשים ברוחבי-ביט גבוהים יותר הדורשים משאבי FPGA נוספים, ולכן הם רק אפשריים ב-FPGA מצוי בעל אורך מסנן מוקטן משמעותית.

הדמיה של המסנן המתואם והמפענח הניצב המשולבים

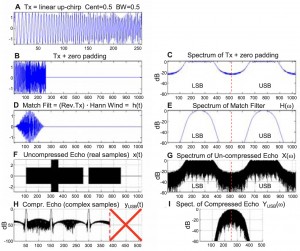

איור 7 מראה הדמיה של MatLab של המסנן המתואם והמפענח הניצב כמתואר בפרק “מסנן מתואם ומפענח ניצב”, אך עם כל האותות והתהליכים בעלי נקודה צפה.

כל הצירים האופקיים הם מספרי אינדקס ולא ערכים מוחלטים במטרים או בהרצים. העמודה השמאלית מראה סדרת-זמן. העמודה הימנית מראה את הספקטרומים Fourier המתאימים עם 0 הרץ במרכז, כלומר הצד הימני של הספקטרומים מייצג את ה-USB.

העקומות A ו-B מראים קוד פולס; ציוץ-על (up-chirp) ליניארי, באורך 256 דגימות, הממורכז במחצית Nyquist ובעל רוחב-פס תדר השווה למחצית Nyquist.

העקומה D מראה את היענות הפולס של המסנן המתואם, הכוללת חלון נתונים Hanning כדי לבטל את אונות הצד של דחיסת הפולסים האופייניים לאות מסוג ציוץ. ההיענות הייתה מאופסת עד לאורך ההד המודגם, שהוא 1024 בהדמיה זו.

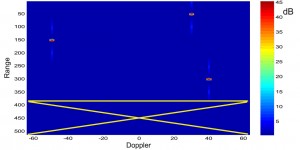

העקומה F מראה את ההד משלוש נקודות פזורות בעלות עצמה שווה הממוקמות בטווחים 100, 300 ו-600 בהתאמה ועם תדרי דופלר של 30, -50 ו-40 בהתאמה. תדרי הדופלר תואמים לתהליך דופלר המבוסס על 128 פולסים, כלומר לספקטרום הדופלר המעובד יש 128 תאים המסומנים מ–64 עד +63. תדרי הדופלר אינם ברורים באיור 7, אך הם מיוצגים בתמונת הטווח-דופלר באיור 8.

באיור 7, העקומות F עד I מראות את כל 128 הפולסים המוספים. איור 7-H מראה את פרופילי הטווח הדחוס, ולכן האינדקס של מחצית הטווח הנובע מהפענוח הניצב. פרופילי הטווח הדחוס הוזזו שמאלה בגודל השווה לכמיסות (latency) המסנן, כלומר לאורך הפולס המשודר. דבר זה משאיר פער בעל גודל דומה בקצה האחורי, המסומן בצלב אדום.

איור 8 מראה את תמונת דופלר-טווח הנובעת מעיבוד דופלר של 128 פרופילי הטווח הדחוס באיור 7-H. עיבוד הדופלר משתמש בחלון נתונים Hanning, כדי להקטין כל אונות-צד הנגרמות על-ידי זליגה ספקטראלית. שטח הטווח המסומן על-ידי הצלב הצהוב מתאים לצלב האדום של איור 7-H.

ניצול וביצועים של משאבי ה-FPGA

כמתואר באיור 6, המכפלה המרוכבת (XUSB(ω)xHUSB(ω והמכפלות המרוכבות בתוך ה-FFT וה-IFFT מנצלות את כפולות החומרה 18 ביט ל-18 ביט, ה-MULT18x18, הזמין בארכיטקטורת Virtex II של Xilinx.

שלושת זיכרונות ה-FIFO הממומשים ב-FPGA מבוססים על רכיב החומרה (Block-RAM (BRAM. בנוסף ליבת ה-FFT משתמשת בכמות משמעותית של BRAM כדי לשמר את הנתונים במהלך החישוב.

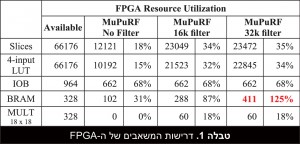

סיכום של משאבי ה-FPGA הדרושים עבור מערכת ה-MuPuRF מוצג בטבלה 1. העמודה השנייה מראה את המשאבים הזמינים. העמודות הבאות מראות את דרישות המשאבים עבור שלושה מקרים שונים: ללא מימוש של מסנן מתואם, עם מסנן מתואם בעל 16 kSamples ועם מסנן מתואם בעל 32 kSamples. כפי שניתן לראות, מספר תאי ה-BRAM הזמינים במעגל ה-Virtex-II Pro מגביל את האורך המרבי של מסנן המתואם ל-16 kSamples.

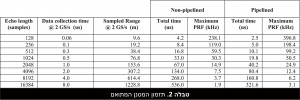

השהית התהליך של המסנן המתואם מגבילה את ה-PRF המרבי של המערכת. טבלה 2 מראה את הקשר בין אורך ההד שיש לעבד וה-PRF המרבי. מוצג בה התזמון של הן הפעלה ללא צינור עיבוד נתונים (non-pipelined) והן עם צינור זה (pipelined) של המסנן המתואם. במוד עם הצינור ליבות ה-FFT מאפשרות לנתונים החדשים להיות מוזזים פנימה באותו הזמן עם ההזזה החוצה של נתוני התוצאות. ביצוע פעולות אלה בו-זמנית מעלה את הביצועים של המסנן בכ-40% בהשוואה למוד ללא צינור. זמן איסוף הנתונים בעמודה מס’ 2 מציין תרחישים המתחילים בטווח אפס. אם התרחישים אמורים להתחיל במורד הטווח, יש להוסיף לזמן הכולל 1 מיקרו-שנייה ל-150 מ’, דבר המוריד את ה-PRF המרבי בהתאמה.

סיכום מפרטים

סיכום המפרטים עבור מערכת המכ”ם MuPuRF מוצג בטבלה 3’. הנתונים עבור המגבר נמוך-הרעש, מגבר ההספק ושבחי האנטנה אינם כלולים.

תוצאות הקרינה בחלל החופשי

מוד המכ”ם MuPuRF נבדק בניסוי קרינה בחלל החופשי. הניסוי השתמש בשתי גרסאות של המסנן המתואם לשם השוואה. נמצא שהמסנן המתואם הממומש ב-FPGA נתן תוצאות זהות מעשית למסנן מתואם בעל נקודה צפה הממומש בתוכנה ב-PC.

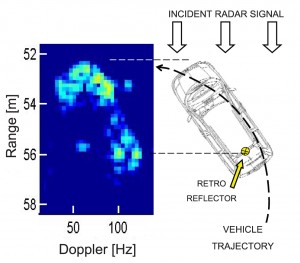

כמטרת המכ”ם שימשה מכונית אשר נעה בשטח בחזית המכ”ם במרחק של 50 מ’ בערך מהאנטנות. האנטנות מוקמו במרחק 3 מ’ זו מזו. הגיאומטריה מוצגת בחלק העליון של איור 9. המכונית נשאה מחזיר אחורי פינתי קטן מותקן על הגג סמוך לחלק האחורי. האנטנות היו בגובה כ-4 מ’ ביחס למישור האדמה של המכונית, והופנו מעט כלפי מטה. שתי האנטנות היו אנטנות קרן מקוטבות אופקית עם אונה ראשית בערך 250 3 dB. ההספק המרבי במחבר בין המשדר לאנטנות היה כ-20 מילי-ואט. בשל הטווח הקצר, לא הופעל LNA. הפרמטרים האחרים של המכ”ם היו כמתואר בטבלה 4.

תמונת הדופלר-טווח באיור 9 היא חפיפה של שלוש תמונות שונות, עם המכונית בשלושה מיקומים שונים כמתואר במרשם הגיאומטריה. כל אחת משלוש תמונות אלו מבוססת על 128 פולסים, במרווח של 0.256 שניות. קו האפס-דופלר הוא תוצאה של מבנים ומכוניות חונות בתוך זירת התרחיש, כמו גם של הקרקע עצמה. איור 9 היא הגדלה של הטווח, ומראה כ-20 מ’ מתוך האורך הכולל של זירת האירוע.

איור 10 הוא הגדלה נוספת הן בטווח והן בדופלר ומתאים לתמונה העליונה מבין שלוש התמונות באיור 9.

יש לציין שהתמונות הן תמונות דופלר-טווח טהורות, ללא עיבוד ISAR כלשהו. מרווח עיבוד הדופלר הקצר ביחס למהירות הנמוכה יחסית של כלי-הרכב של כ-8 קמ”ש יוצר מריחה מועטת ביותר של התמונות. ניתן לזהות בנקל את קווי המכונית, כמו גם את המחזיר האחורי הפינתי.

סיכום ומסקנות

כרטיס ה-COTS TRITON VXS-1 הוכיח עצמו כפלטפורמת חומרה מתאימה לביצוע המשימות בפס-בסיס בזמן-אמת הדרושות במוד המכ”ם של מיתקן ההמחשה RF רב-משימתי המתוכנן. המכ”ם נבדק בניסוי קרינה בחלל החופשי עם מסנן מתואם ומפענח ניצב ממומשים ב-FPGA, ונתן תוצאות משביעות רצון במלואן עבור צורת-גל של רוחב-פס של 900 מגה-הרץ. הרזולוציה בטווח התיאורטית עבור רוחב-פס זה היא 17 סמ’, נתון התואם יפה את רזולוציית הטווח שנרשמה.

ה-TRITON הוא ללא ספק מתאים עבור הפונקציות והמודים המתוכננים הנוספים של מערכת ה-MuPuRF, והעבודה למימושם תימשך.

הבעת תודה

המחברים מבקשים להודות ל-Steinar Johnsrud מ-FFI עבור הרכבת יחידת הממיר מעלה-מוריד RF.

הכתבה נמסרה באדיבות חברת DAN-EL.

סימוכין

[1] (2008) Triton VXS-1 data sheet. [Online]. Available: www.tekmicro.com/PDFs/triton0507.pdf

[2] (2008) The Tekmicro website. [Online]. Available: www.tekmicro.com

[3] N. Levanon, Radar Principles, New York, USA: John Wiley & Sons, 1988.

[4] (2008) Xilinx Coregen Fast Fourier Transform v5.0 data sheet [Online]. Available:http://www[.xilinx.com/ipcenter/catalog/logicore/docs/xfft.pdf