מאת:| ריק אידס, Agilent Technologies

מאת:| ריק אידס, Agilent Technologies

תקציר:

במאמר זה משתף ריק אידס – מנהל תוכנית ®PCI Express של חטיבת הבדיקות הדיגיטליות ב-Agilent וחבר מועצת ®PCI-SIG – את דעותיו בנוגע לביקוש הנוכחי והבלתי נדלה לרוחב פס, ומתאר כיצד יוכלו תקני PCI Express 3.0 המתגבשים לסייע למהנדסים בהתמודדות עמו. הוא מסביר את היתרונות הנלווים לכמה מן התכונות והיכולות החדשות הגלומות בטכנולוגיית Gen 3 ודן באתגרים שעמם צפויים המהנדסים להתמודד בעת בדיקה של התקניהם החדשים. בנוסף, ריק מתייחס גם לחשיבות התקנים הדיגיטליים ולתפקיד הקריטי השמור למומחיות בתחום המדידה לאורך תהליכים המאפשרים יכולת פעולה הדדית.

אם ראיתם את הסרט “חנות קטנה ומטריפה”, מן הסתם זכור לכם הצמח הטורף – אודרי II – הדורש לקבל את מזונו, כשהלחץ והזעם בקולו הולכים וגוברים בהדרגה.

האינטרנט, על תאבונה שאינו יודע שובע לרוחב פס, ראויה ללא ספק לשם “אודרי III”.

הגל החדש של מחשוב בענן, יישומי גיימינג מקוונים עתירי גרפיקה וזרימת וידאו מניעים את הרעב המטורף לרוחב פס. קראתי לאחרונה, כי בשנה שעברה ייצרה יו-טיוב תעבורת אינטרנט שהייתה שווה בהיקפה לתעבורה שייצרה האינטרנט כולה לפני עשור. מה יקרה אפוא כשיו-טיוב תתחיל לספק סרטוני וידאו בתלת-ממד ובאיכות 1080P? ככל שהאיכות עולה, כך נידרש לבצע העברה של נתונים רבים יותר. אודרי III תאבד שליטה לחלוטין.

בנוסף לביקוש האדיר לרוחב פס, גם מאגרי ה”צנרת” המיועדים להעברת כמות הסיבים האדירה הולכים ואוזלים. לפני עשר שנים, הענף היה כמרקחה, שכן 90 אחוזים מכלל הסיבים שנפרסו בשנות ה-90 היו במצב “האפלה” – דהיינו, הם היו אמנם פרוסים בשטח, אבל נותרו ללא שימוש. כיום, הסיבים כולם “מוארים”. הוספת סיבים או מעבר לטכנולוגיה אופטית יכולים לעזור, אבל מדובר בפתרון יקר.

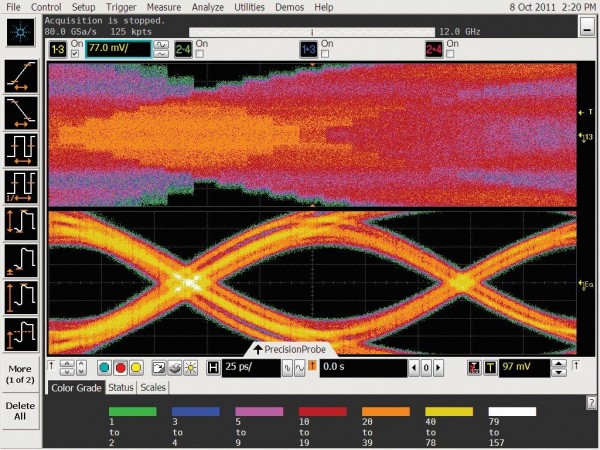

בגין הפסדים בערוצים גבוהי תדרים, אות ה-PCIe 3.0 שבסוף הערוץ הוא “עין סגורה” (חלק עליון). נדרשת אקווליזציית CTLE של הרסיבר.

בקצבים של GBit/s , תקן PCI Express 3.0 עושה שימוש באקווליזציה נרחבת מבוססת משדר (de-emphasis) לצורך קיזוז הפסדי הערוצים בתדרים הגבוהים.

אפיק ה-PCI Express מקדם את רוחב הפס

הדור האחרון של טכנולוגיית PCI Express® – Gen 3 – צפוי לסייע בהתמודדות עם הביקוש לרוחב פס אחר. כאשר הציגה אינטל את אפיק ה-PCI Express 1.0 הטורי בשנת 2004, התקן סיפק רוחב פס מקורב של 6.4 GB/s – שיפור לא מבוטל לעומת האפיקים המקביליים שבהם נעשה שימוש באותה עת. טכנולוגיית PCI Express Gen 1 עדיין נפוצה למדי – וכמעט זמינה בכל מקום. כיום היא כה זולה – לא חינמית אמנם, אבל קרובה לכך – עד שהיא משולבת במוצרי צריכה יומיומיים, החל במכונות קפה וכלה במכונות תפירה.

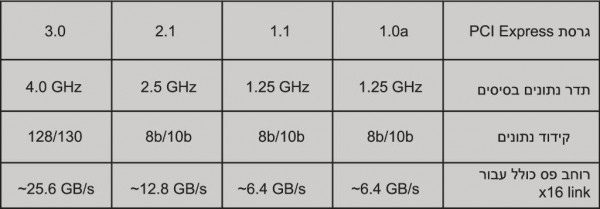

הגרסה הנוכחית של PCI Express – 3.0 – הלכה בעקבותיה של PCIe 2.1 והכפילה את תפוקת רוחב הפס על-ידי שינוי סכמת הקידוד שבה נעשה שימוש בגרסאות PCIe 1.x ו- גרסת Gen 3 תניב רוחב פס כולל מקורב של . שיפור של פי 4 בתפוקה המושג בתוך 6 שנים הוא בהחלט משמעותי – ומדובר ללא ספק בשיפור שהגיע בזמן.

הגידול ברוחב הפס מאפשר למפתחים ולמתכננים להטמיע interconnects (חברור) צרים יותר, לשפר את הפרודוקטיביות ולהפחית עלויות. תקן PCI Express 3.0 מתאפיין בתאימות לאחור עם גרסאות 2.0, 1.1 ו-1.0a, כך שההתקנים ולוחות האם שיתוכננו עבור Gen 3.0 יעבדו גם עם תקנים קודמים. התקן שיפר את פרוטוקול העברת הנתונים Point-to-Point ואת ארכיטקטורת התוכנה שלו, ומתאפיין בסבילות רבה יותר לבדיקות ריצוד ובחון (PROBING).

טכנולוגיית Gen 3 תיפרס תחילה ביישומי גרפיקה המיועדים לקצה העליון, שצרכניהם מעוניינים בהתנהגות “ריאליסטית” יותר על המסך – לדוגמה, מחשבי גיימרים. במגזר שוק זה, הצרכנים מוכנים לשלם תמורת לוחות איכותיים ויקרים.

מרחב השרתים הוא מגזר שוק נוסף, שבו צפוי תקן PCI Express 3.0 לזכות בהצלחה משמעותית. טכנולוגיית PCI Express Gen 3 מאפשרת לשלב ביצועים ברמת x16 Gen 2 בגורם צורה של x8. בדרך כלל, תכנוני השרתים מוגבלים במקום ולעתים מזומנות כרטיסי x16 פשוט גדולים מדי. כרטיסי הממשק מסוג x8 LAN צפויים לספק ביצועים של . נראה, כי זה יהיה אחד מהכוחות המניעים המשמעותיים ביותר עבור טכנולוגיית PCI Express Gen 3.

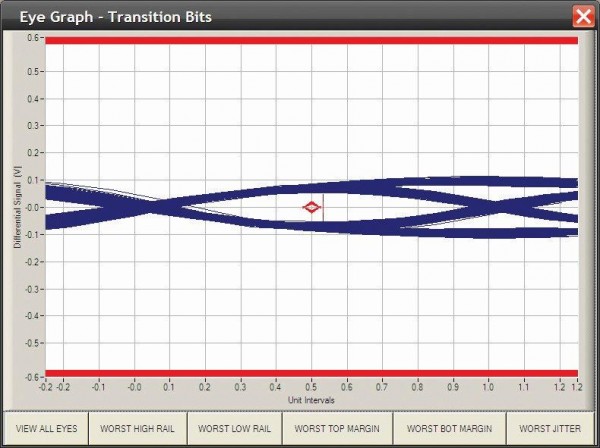

זו דיאגרמת עין של סיבית ההעברה עבור אות PCI3 3.0 ממשי. גם לאחר שבוצעה אקווליזציית CTLE ו-DFE, גובה העין נמוך בצורה משמעותית לעומת Gen2.

אתגרי תקן PCI Express 3.0

המעבר ל-PCI Express 3.0 יהווה אתגר עבור מעבדות אימות ומהנדסי בדיקה רבים, שכן התקן מטמיע מהירויות גבוהות יותר תוך שהוא מתיימר לתמוך בטופולוגיות ובאורכי ערוצים זהים. הטכנולוגיה החדשה אף כרוכה בשינוי מוחלט של סכמת הקידוד ומתאפיינת בתכונות מתקדמות של פרוטוקולים.

מבחינה ארכיטקטונית, ממשק PCI Exp Gen 3 עובר מאפיק SOUTH BRIDGE למעבד הראשי עצמו. המשמעות של ארכיטקטורה זו היא, כי ה-trace links עשויים להיות ארוכים מעט יותר וכי הדבר עלול להפוך את ניתוב האותות למעט מורכב יותר, אולם כך יימנעו זמני ההשהיה הקשורים ב-SOUTH BRIDGE. יצרני השבבים יידרשו לשקול ולקזז את הביצועים לעומת מורכבות הניתוב.

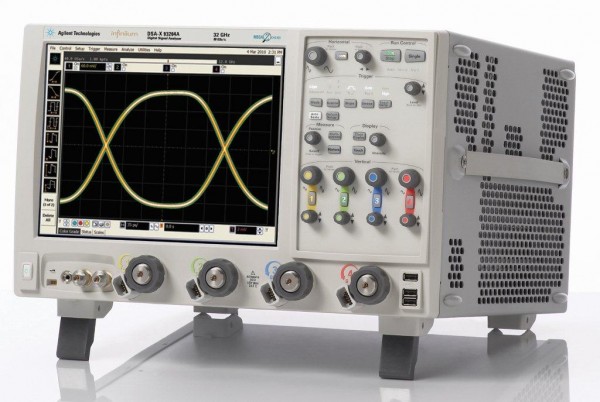

באופן כללי, יהיה קשה יותר לבדוק את התקני ה-PCI Express 3.0 מאשר את התקני Gen 2. בכל הנוגע למפרט הבסיס של טכנולוגיית Gen 3, איננו צופים שהמהנדסים יבצעו מדידות בפינים באופן ישיר, שכן הלחמת הבחון לפין עלולה לגרום יותר בעיות מאשר הן יפתרו. במקום זה, המהנדסים יצטרכו ליצור לוחות עם מסלול מדויק נוסף (ערוץ ה-breakout) המתפצל מהמסלול הראשי כך שאותות ה-PCI Express יובאו לסביבת מדידה דרך חיבורים ועקבות עכבה מבוקרות.

בעת שימוש בגישה זו, יש להסיר מתוצאות המדידה את השפעות ניחות המעבר (insertion loss) של ערוץ ה-breakout. ה-PCI-SIG ממליצה למהנדסים ליצור ערוצי “רפליקה”, אשר משכפלים את העקבות באופן שמקל על השימוש ב-TDR או ב-VNA לצורך חישוב ההשפעות תלויות התדר.

כדי להשיג קצב של GT/s בחומר FR4 PCB, יהיה עליך להכיל אקווליזציה בתוך המקלט. בעת פעולה בתדרים גבוהים, רוב תכולת התדרים שמעל 8 גה”צ עוברת ניחות על-ידי הערוץ, כך שאין לכך השפעה רבה מדי על המקלט. הדבר מקל על פעולת ההסרה (de-embedding), כיוון שבמקרים מסוימים היצרנים מבצעים הסרה רק עד ל-8 גה”צ והשפעות הרעש של התדרים הגבוהים, אשר עלולות בדרך כלל להיגרם על-ידי פעולת ה-de-embedding, מוגבלות למעשה.

מדוע יש חשיבות לתקנים

נוכח העובדה שהתדרים ורוחבי הפס הופכים גבוהים יותר, על גופי התקינה לקחת בחשבון את דרישות הבדיקה והמדידה בעת כתיבתם של מפרטים חדשים. אם לא יעשו כן, ייתכן שהמהנדסים לא יצליחו לבדוק את התקניהם כדי לוודא תאימות למפרט. המדידות נדרשות לצורך אבחון בעיות ואימות החלתם של הפתרונות הנכונים.

Agilent היא חברה תורמת ופעילה ב-PCI-SIG ומכהנת במועצת המנהלים של הקבוצה. ציוד של Agilent נמצא בשימוש בסדנאות התאימות של ה-PCI-SIG, ומאפשר לאמת את ציות החברות למפרט ה-PCI Express. מעורבותה של Agilent בתקנים אלה מבטיחה למהנדסי התכנון שני יתרונות מרכזיים:

ראשית, היא מאפשרת לספק לשוק את המוצרים הנכונים, כאשר המהנדסים זקוקים להם.

שנית, בזכות מעורבותה של Agilent ב-plug-fests, סדנאות וסמינרים, החברה נמצאת בעמדה ייחודית שמאפשרת פיתוח פתרונות אשר מתפתחים במקביל לתקנים וכך מעניקים למהנדסים את היכולת לתכנן את מוצריהם בביטחון מלא.

תקני PCI Express החדשים יאפשרו למהנדסים להגדיל את רוחב הפס והתפוקה, ולהשביע את רעבונה של אודרי III – לפחות לעת עתה. Agilent מצוידת בכלי הבדיקה והמדידה הנדרשים, אשר יסייעו למהנדסים להתגבר על האתגרים ולהאיץ את תהליך הפיתוח של התקני Gen 3 החדשים.

PCI Express ו-PCI-SIG הם סימני מסחר רשומים ו/או סימני שירות של PCI-SIG.