מבוא

דרישת הצרכנים למוצרים מהירים יותר, טובים יותר, מקדמת את החדשנות לרמות בלתי-מוכרות בעבר. מתכנני מערכות ניצבים לכן בפני דילמה משותפת: לתכנן מוצר חדש על פלטפורמה ידועה, תוך ביצוע שנויים קטנים בלבד; או להשתמש בפלטפורמה חדשה לחלוטין בעזרת המוצרים והיכולות המתקדמים ביותר. הדבר הראשון עשוי להיות מהיר וללא-סיכון, אך הוא מציע גמול נמוך; בעוד האחרון מציע רב-צדדיות, פונקציונליות וערך יותר טובים, אך תוך כדי סיכון גבוה יותר.

עתה, מערך חדש של כלי הדמיה מאפשר ביצוע אב-טיפוס בתוכנה, תוך מזעור סיכון הפיתוח ומתן למתכננים את האמונה שמוצריהם החדשים יתפקדו כמצופה. התוכנה מציעה מבט לתוך היכולות של מוצרים יחידים כגון ממירים אנלוגי-לדיגיטלי, מעגלים משולבים של שעונים ומגברים, ומאפשרת לשלב התקנים (ADCs ושעונים לדוגמה) ללא הצורך להשיג רכיבים ממשיים. את ההחלטה לרכוש חומרה ניתן לקבל לאחר שהערכת התוכנה הושלמה, דבר החוסך זמן וכסף.

מאמר זה מוכיח את הרב צדדיות של

ה-™ADIsimADC™, ADIsimCLK וערכת התוכנה ®VisualAnalog כדי לחזות ביצועי ADC בשילוב עם שעון דגימה. הדוגמא משתמשת בממיר אנלוגי לדיגיטלי 16-bit, 250-MSPS AD9467 ומחולל השעון בעל ריצוד נמוך AD9523. הפרק הראשון מתאר את הערכת התוכנה, תוך הדמיית ביצועי ה-ADC לפי התדר והצגת הדרך כדי לחבר את ההתקנים בתוכנה. הפרק השני מפרט מערך חומרה בעולם הממשי, תוך שימוש בכרטיסי הערכה ותוכנת SPIController. הדוגמא מכוונת שעון

ה-AD9467 ב-245.76MSPS. כרטיס ההערכה AD9523-1 משתמש ב-GUI אינטראקטיבי כדי לעצב את מוצאי השעון.

הדמיית-יחד תוך שימוש

ב-ADIsimADC ו-ADIsimCLK

ראשית, הורד והתקן VisualAnalog ותוכנת ההערכה . ADIsimADC מזווד ביחד עם VisualAnalog. עם אתחול VisualAnalog, חלון pop-up יבקש את המשתמש לבחור קנבס (canvas), כמתואר באיור 1.

הדגם ADIsimADC עבור ה-AD9467 זמין לפי בחירת התפריט ADCSingleAD946.

איור 2 מראה את קנבס ה-ADIsimADC Average FFT.

התקנת ה-ADIsimADC כדי לחזות התנהגות ה-ADC

חבר תדר בגוש Tone Generator ולחץ על . ADIsimADC ממיר אוטומטית תדר זה לתדר קוהרנטי המבוסס על קצב הדגימה וגודל הדגימה. איור 3 מראה את ה-FFT של מבוא חד-צליל ב-9.7 מגה-הרץ תוך שימוש בקביעות מחדל.

קביעת ADIsimCLK לשם חיזוי התנהגות ה-AD9523-1

שנית, הורד והתקן את תוכנת ה-ADIsimCLK. לאחר ההתקנה פתח את התוכנית ובחר FileNew. חלון מופיע עם בחירת ההתקנים, כמתואר באיור 4.

עקוב אחר שיטת העריכה הדומה ביותר למימוש המערכת המכוונת. בדוגמא זו, שעון חיצוני של 30.72 מגה-הרץ מספק את הייחוס ל-PLL הראשון. Crystek CVHD-950 משמש כ-VCXO עבור הלולאה הראשונה של ה-PLL כפול-הלולאות. תדר ה-VCO הפנימי מכוון ל-2949.12 מגה-הרץ ומחולק פנימית ב-3. מחלק ב-4 על OUT7 מספק את שעון ה-245.76 מגה-הרץ. התקנה זו מוצגת באיור 5.

ADIsimCLK מפיק גם דוח על מוצאי השעון, כולל רעש מופע במוצא וריצוד בתחומי שילוב שונים. דוחות אלה זמינים לפי הסימנים המתאימים למוצאים השונים. בהתקנה זו, OUT7 משמש לכיוון השעון של כרטיס ההערכה AD9467. עמוד הדוח מוצג באיור 6. מפרט-המפתח, ריצוד בפס רחב, מודגש.

הדמיית AD9467 עם ה-AD9523-1

ADIsimADC יכול לחזות את ביצועי

ה-AD9467 כאשר מתוזמן עם ה-AD9523-1. ניתן להעביר את מפרט הריצוד רחב-הפס מדוח ADIsimCLK לקנבס ה-ADIsimADC. בקנבס ה-FFT, גוש ה-ADC Model מאפשר למשתמש לעדכן את מפרט הריצוד הכולל, כמוצג באיור 7.

הריצוד הכולל ניתן לחישוב כריבוע סכום השורשים (root-sum-square-rss) של רכיבי הריצוד הפרטניים. במקרה זה, ריצוד הפתח הוא 60fs וריצוד הפס הרחב הוא 215fs. ריצוד ה-rss המועבר

ל-ADIsimADC הוא 223.2fs, המייצר את ה-FFT חד-צליל בעל 97 מגה-הרץ המוצג באיור 8. על ידי שימוש בריצוד המעודכן, ADIsimADC יכול לחזות את הביצועים הצפויים בכל תדר מבוא.

הערה קצרה על ריצוד

ADC צריך לדגום במסודר דגימות של אות אנלוגי. דרוש שעון דגימה יציב, מאחר שכל מקור שעון לא אידיאלי יצור רעש מופע כלשהו. ריצוד הוא שילוב של רעש המופע לאורך המחזור בין שני היסטי תדר מוגדרים מנושא (carrier) שעון הדגימה. עבור ADCs רעש רחב-פס נחשב ככלל החשוב ביותר. ADIsimCLK מחשב את הריצוד רחב הפס, המשלב את רעש המופע מעל היסט של 1 קילו-הרץ. ריצוד רחב-פס זה מועבר לדגם ה-ADIsimADC כדי להבין את השפעת הריצוד על ביצועי ה-ADC. לשם מידע מפורט יותר על כיצד ריצוד שעון הדגימה משפיע על ביצועי ה-ADC נא להתייחס לAN-756 Application Note: Sampled Systems and the Effects of Clock Phase Noise and Jitter.

ביצועים מדודים

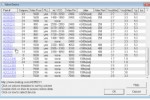

חיזוי ה-ADIsimADC נבדק תוך שימוש בכרטיס ההערכה AD9467 וכרטיס ההערכה AD9523-1. ה-AD9523-1 עוצב כדי ליצור שעון LVPECL של 245.76 מגה-הרץ על OUT7. מוצא זה חובר לכרטיס ההערכה AD9467, אשר שונה כדי לקבל מבוא שעון הפרשי על J200 ו-J201. התקנה זו מוצגת באיור 9.

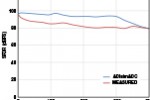

איור 11 מראה את נתוני ה-SFDR. מספרים אלה אינם תואמים במלואם, אך המגמה הכוללת בין הנתונים הדמויים והמדודים לפי תדר מתאימה היטב. SFDR תלוי מאוד במערך כרטיס ה-PC, הרכיבים, אמפליטודת השעון, דבר היכול להסביר את ההפרש.

מדידה טובה יותר של העיוות תשווה בין הנתונים הדמויים והמדודים עבור עיוות הרמוני שני ושלישי, כמוצג באיור 12 ואיור 13. ביצועי ה-HD2 הדמויים והמדודים תואמים היטב, דבר המוכיח שהאות ההפרשי המגיע ל-ADC בכרטיס ההערכה מאוזן היטב במונחים של אמפליטודה ומופע ושהמערך של כרטיס ההערכה הוא טוב דיו כדי לא להשפיע משמעותית על איזון האות ההפרשי.

מצד שני, חיזוי HD3 לפי תדר יכול להיות מטעה. דגם ה-ADIsimADC מפותח על די הסתכלות בביצועי ה-ADC ונתוני ה-DNL במהלך האיפיון. האלגוריתם משתמש בטכניקות של שרבוב וחיוץ כדי לחזות תחום דינמי בתדרים מסוימים, אך אינו יכול לחזות במדויק את ביצועי ה-HD3 בכל הנקודות.

ביצועי ה-HD3 המעשיים תלויים מאד בגורמי העולם הממשי, כגון מתח הספקה, בחירת רכיבים, חוצץ מבוא ADC, ואיכות אות השעון.

חיזוי ה-HD3 עלול לא להיות תמיד מדויק, אך המגמה הכוללת לפי התדר מספקת התאמה טובה בין הנתונים הדמויים והמדודים.

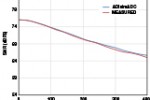

בתכנוני מערכת רבים, מדידת ביצועי הראשית היא ה-SNR. ה-SFDR והתחום הדינמי תלויים בגורמים אחרים רבים. ערכי ה-SNR בין ההדמיה והנתונים המדודים תואמים היטב, דבר המקנה למתכנני המערכת ביטחון בבחירת ה- ADC והשעון.

סיכום

הצורך במחזורי תכנון קצרים יותר מציב לחצים עצומים על מתכנני המערכת להעריך מוצרים חדשים עבור התכנונים שלהם. הערכת החומרה היא כמעט תמיד הכרח, אך הבחירה בשילוב חומרה לא נכונה עלולה לעלות כסף וזמן. הערכת התוכנה יכולה לפעול כמבט ראשון מהיר וקל במוצרי ADC .ADIsimADC

ו-ADIsimCLK מציעים דרך פשוטה ויעילה עבור מתכנני המערכת לבחור ADC ומעגל משולב לשעון. כלי תוכנה אלה מאפשרים למתכנני המערכת לערב ולהתאים ADCs שונים ומעגלי שעון, דבר המאפשר לפתח מספיק אמון ברכיבים הנבחרים כדי לבצע הערכת חומרה.

הבעת תודה

תודה ל-Jillian Walsh עבור העבודה הקשה באיסוף המעבדתי של הנתונים עבור מאמר זה ותודה ל-Kyle Slightom עבור העזרה בכרטיס ההערכה של ה-AD9523-1 והתקנת התוכנה.

סימוכין

Brannon, Brad and Tom MacLeod. AN-737 Application Note.

How ADIsimADC Models an ADC. Analog Devices, Inc., 2009.

Brannon, Brad. AN-756 Application Note. Sampled Systems and the Effects of Clock Phase Noise and Jitter.

Analog Devices, Inc., 2004.

Analog Devices High Speed Converter Division. AN-878

Application Note. High Speed ADC SPI Control Software.

Analog Devices, Inc., 2007.

AN-905 Application Note. VisualAnalog™

Converter Evaluation

Tool Version 1.0 User Manual.

MT-003 Tutorial. Understand SINAD, ENOB, SNR, THD,

THD + N, and SFDR so You Don’t Get Lost in the Noise Floor.

Reeder, Rob. “Test High-Speed ADCs for Analog-Input Phase

Imbalance.”Test & Measurement World,2011.

Slightom, Kyle. “Dual-Loop Clock Generator Cleans Jitter,

Provides Multiple High-Frequency Outputs.” Analog Dialogue

Volume 48, Number 1, 2014.

על המחבר:

Umesh Jayamohan הוא מהנדס יישומים בקבוצת High Speed Converter Group של Analog Devices ב-Greensboro, NC.

- איור 1. חלון VisualAnalog New Canvas

- איור 2. קנבס ADIsimADC המראה את AD9467 עם FFT חד-צליל ב- 9.7 מגה-הרץ

- איור 3. FFT חד-צליל ADIsimADC ב-9.7 מגה-הרץ

- איור 4. בחירת התקן ADIsimCLK

- איור 5. התקנת AD9523-1 ב-ADIsimCLK

- איור 6. דוח OUT7 ב- ADIsimCLK

- איור 7. עדכון הריצוד בדגם ADIsimADC

- איור 8. FFT חד-צליל במבוא 97 מגה-הרץ עם מפרט ריצוד מעודכן ב-ADIsimADC

- איור 9. התקנת חומרה המראה את כרטיסי ההערכה AD9467 ו-AD9523-1.

- איור 10. SNR כנגד תדר מבוא אנלוגי המשווה בין ADIsimADC והנתונים המדודים המעשיים

- איור 11. SFDR כנגד תדר מבוא אנלוגי המשווה ADIsimADC ונתוני מדידה מעשיים

- איור 12. HD2 לעומת תדר מבוא אנלוגי המשווה ADIsimADC ונתוני מדידה מעשיים

- איור 13. SFDR כנגד תדר מבוא אנלוגי המשווה ADIsimADC ונתוני מדידה מעשיים