טכנולוגיית 20 ננו-מטר מהווה הזדמנות ענקית עבור OEM באלקטרוניקה. כל הסימנים מצביעים על שיפור בביצועים של 30-50%, חיסכון בהספק דינמי של 30% והקטנת השטח של 50% בהשוואה לטכנולוגיית 28 ננו-מטר. טכנולוגיית 20 ננו-מטר תאפשר הפקת דורות חדשים של מוצרים קטנים יותר, מהירים יותר ו”ירוקים” יותר בתחומים כגון מחשוב נייד, טלפונים חכמים, בידור והתקנים אלחוטיים. מעבר מוקדם ל-20 ננו-מטר יהווה עבור OEM יתרון תחרותי, במיוחד בשוק הצרכני.

אך טכנולוגיית 20 ננו-מטר יוצרת גם אתגרים משמעותיים חדשים בתכנון ובייצור. כדי להפוך את ה-20 ננו-מטר לבר-ביצוע, כלי התכנון והתהליך חייבים להשתנות באופן יסודי. לדוגמה, גישה סידרתית מבוססת-כלים נקודתיים לא תעבוד יותר, משום שהשלבים השונים של מחזור התכנון הם הרבה יותר תלויים זה בזה מאשר היו בטכנולוגיות תכנון קודמות. במקומם, דרושים תהליכים משולבים מקצה-לקצה.

יתר על כן, הגישה המסורתית “תקן בסוף” צריכה להיעלם לטובת מתודולוגיה של ” מניעה, ניתוח, אופטימיזציה” המתקנת תוך כדי היישום, ובכך מונעת תקופה ארוכה של תיקונים בסוף. לבסוף, תהליך 20 ננו-מטר מלא חייב לתמוך גם בתכנון מותאם/אנלוגי וגם בתכנון דיגיטלי. זאת משום שכמעט כל (systems-on-chip- SoC) של 20 ננו-מטר יהיו בעלי אות מעורב, ותכנון דיגיטלי לא יכול להתחיל לפני שכל ספריות התאים של 20 ננו-מטר קיימות.

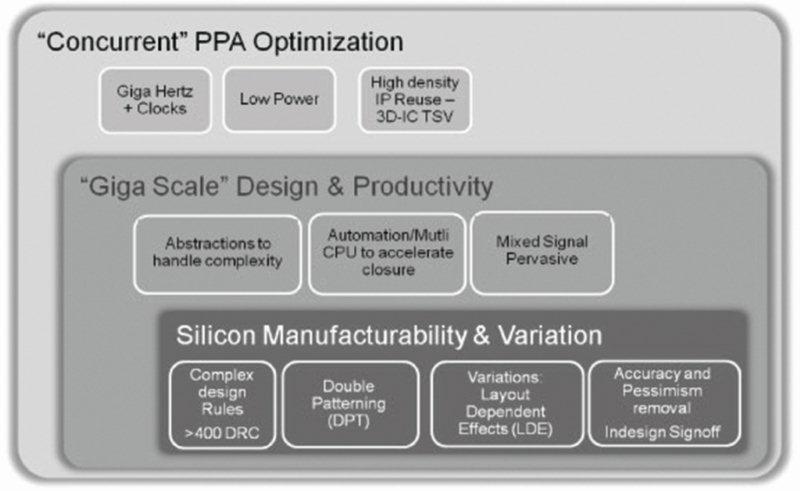

סביר שהאתגר המדובר ביותר של התכנון ב-20 ננו-מטר הוא השימוש ב-הדפס כפול (double patterning), המשתמש במסכות נוספות כדי להתגבר על המגבלות של ציוד הליתוגרפיה הקיים. אולם, אתגרי ה-20 ננו-מטר מכוונים הרבה יותר רחוק מההדפס הכפול. במבט רחב יותר, טכנולוגיית 20 ננו-מטר מציבה דרישות בשלושת התחומים הבאים:

יכולות הייצור והשונות (variation) בסיליקון. ב-20 ננו-מטר, ההשתנות (variability) היא בכל מקום, והרבה ממנה תלוי ב”הקשר” התסדיר (layout) בתוכו מוקמו התאים וההתקנים. ישנה הדדיות עמוקה ומורכבת בין יכולות היצור והשונות. השימוש בהדפס כפול הוא חלק מהדדיות זאת, וכל צעד בתהליך התכנון חייב להיות מודע לו .

מורכבות התכנון בסקלה של גיגה. ICsבב-20 ננו-מטר עשויים להכיל 8-12 מיליארד טרנזיסטורים, ולחצי הזמן-לשיווק נהיים רק יותר קשים. כיצד מסוגלים שבבים מורכבים בצורה לא-תיאמן לצאת בזמן? הכלים צריכים לטפל בכמויות עצומות של נתונים, והמודלים נדרשים לספק את רמת הפירוט הנכונה בדיוק עבור כל רמת הפשטה נתונה.

אופטימיזציה בו-זמנית של הספק, ביצועים ושטח. רוב ה-SoCs יהיו בעלי הספק נמוך, וכמעט כולם יכילו מעגלים אנלוגיים/אות מעורב. הספק, ביצועים ושטח לא ניתנים לאופטימיזציה בנפרד, ודבר זה נכון במיוחד כאשר מדברים על שעונים.

להלן מבט קרוב יותר על האתגרים והדרישות בכל אחד מתחומים אלה.

יכולות הייצור

ושונות הסיליקון

ישנם מקורות רבים לשונות ב-20 ננו-מטר. התקני CMOS יותר קטנים, לדוגמה, חשופים לשינוי באורך התעלה וסימום התעלה. אורך החיווט הגדל גורם לעלייה בהתנגדות חוטים והחיבורים האנכיים ביניהם (vias), אשר דורשת בעצמה שינויים בגודל החוטים וטכניקות tapering שונות. המרווחים הקטנים במתכת גורמים לקיבול צימוד גדל בין המוליכים ולכן יכולים לגרום לבעיות של signal integrity.

ב-20 ננו-מטר, מידול הביצועים או ההספק של התקן בפני עצמו עלולים לא לעבוד. תופעות כגון לחץ וליתוגרפיה, מיקום ההתקן בתסדיר – ומה שקרוב אליו – עשוים להיות בעלי השפעה עצומה על ביצועי ההתקן וההספק שלו. התופעה מכונה layout-dependent effect –

(LDE). בשעה שה-LDE היווה בעיה מתהווה ב-28 ננו-מטר, היא חמורה בהרבה ב-20 ננו-מטר, כאשר התאים הרבה יותר קרובים זה לזה. ה-LDE משפיע הן על סביבות תכנון מותאם/אנלוגי והן על הדיגיטלי, אפיוני הספריה, המיקום, החיווט וכלי הניתוח צריכים להתחשב כולם ב-LDE.

לא צריך להפתיע שקיימות כ-5,000 בדיקות של חוקי התכנון (design rule checks- DRC) ב-20 ננו-מטר, כולל 30 עד 40 כללים חדשים עבור הדפס כפול. יש כ-400 כלליo תסדיר חדשים, מתקדמים, עבור שכבות המתכת, ואחדים מהם הם כללי תכנון אגרסיביים ???. כלי התכנון צריכים להתעדכן בחוקים אלה והמתכננים חייבים להיות ערים להם.

הטיפול בהדפס כפול

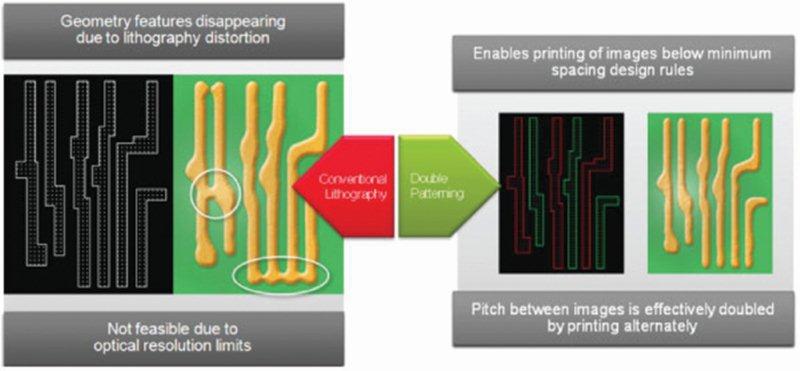

ככלל, השונות היא בעיה מוקדמת ההולכת ומחריפה ב-20 ננו-מטר. הדפס כפול , לעומת זאת, יהווה אתגר חדש עבור כמעט כל צוותי התכנון ב-20 ננו-מטר. טכנולוגיה זו דרושה כדי לגרום שציוד ליתוגרפיה של 193 ננו-מטר ידפיס נכון כאשר מרווחי המתכת הם מתחת ל-80 ננו-מטר. ברוב המקרים, אולם, יהיה צורך בה רק בשכבות מתכת נמוכות יותר.

הנה כיצד הדבר עובד. כאשר לשכבת מתכת יש תבניותסמוכות מידי זו לזו מכדי להפריד בליתוגרפיה של 193 ננו-מטר, הדפס כפול מחלק את השכבה לשתי מסכות נפרדות. כל מסכה נחשפת בנפרד, והחשיפות חופפות כדי ליצור תבניות שהן בעלות מחצית המרווח שניתן היה להדפיס באמצעות ליתוגרפיה של 193 ננו-מטר (איור 2). הדפס כפול דורש אפוא מסכות נוספות, ביחד עם הפרדת התסדיר לשני צבעים הקובעים כיצד התסדיר ימופה ללמסכות.

סוג אחד של מידול כפול הוא litho etch litho etch . זוהי הטכניקה הפשוטה והאינטואיטיבית ביותר – בעקבות הפרדת התסדיר והצביעה, מחצית התבניות הולכות אל המסכה הראשונה ומחצית אל המסכה השנייה. הדפס כפול בעל יישור עצמי (self-aligned double patterning הוא תהליך מורכב יותר הכולל שיקוע מבדדי-מרווח (spacers) במשטחים צדדיים עם תכונות תבליטים, הסרת תכונות התבליטים והוספת חומרים דיאלקטריים לשטחים פתוחים. אולם, הוא מציע רזולוציה מעט טובה יותר. LELE ו-SADP דורשים כל אחד מהם מערך חוקי תכנון משלהם.

הדפס כפול משפיע על כל חלק בתהליך תכנון ה-IC מפיתוח תא תקני עד מיקום, חיווט, חישוב קיבולים ,התנגדויות והשראויותווריפיקציה פיסיקלית. בצד האנלוגי/מותאם, יצירת תאים וספריות צריכה להבטיח שתאים ורכיבי IP תואמים את חוקי התכנון של הדפס כפול. בצד הדיגיטלי, שלב המיקום צריך למנוע ניגודי צבע פוטנציאליים ולמזער את השפעת השטח של הדפס כפול. החיווט חייב להבין כיצד תופרד שכבה אל שתי מסכות ולמנוע תסדירים שלא ניתנים להפרדה חוקית.

חישוב הקיבולים הפרזיטים צריך להיות ער לכך שהסטה קלה בין מסכות תגרום לשינויים. ניתוח התזמון וההספק צריך לטפל ביותר נקודות עבודה ולקבל קבצי Standard Parasitic Exchange Format בעלי ערכים מרובים. הבדיקה הפיסיקלית צריכה להבטיח שההפרדה הסופית לשני צבעים היא מדויקת ושלימה לפני הסגירה.

השיקול החשוב ביותר הוא שהדפס כפול צריך להיבנות בתוך תהליך תכנון “מניעה, ניתוח, אופטימיזציה” תואם 20 ננו-מטר מההתחלה, מיצירת התא מותאם/אנלוגי ל”מיקום וחיווט” דיגיטלי. הדפס כפול יהיה אתגר בר יישום אם הוא אוטומטי ככל האפשר, ואם כלים באיכות-signoff מונעים או מתקנים את מרבית השגיאות לפני שלב הסגירה הסופי.

תכנון ופרודוקטיביות בקנה-מידה גיגה

שבב מורכב איננו שווה הרבה אם הוא איננו מסופק בזמן. תהליכי תכנון IC חייבים לעבור שינויים משמעותיים אחדים כדי לשגר את שבבי 20 ננו-מטר החוצה בזמן ובמסגרת התקציב.

כדי לתכנן גיגה-שבבים של ICs 20 ננו-מטר, צוותי התכנון ישלבו ויבדקו מספר גדול של IP’s אנלוגיים ודיגיטליים. שילוב IP הוא מאתגר, ואף ב-80% שימוש חוזר, יהיה מספר רב של מעגלים חדשים לתכנן ולבדוק. לא תהיה ברירהאלא להשתמש ברמות גבוהות יותר של הפשטה הן עבור התכנון והן עבור הבדיקה, ביחד עם כלים המותאמים לשימוש עם ליבות-מרובות שהם בעלי קיבולת גבוהה, מהירות עיבוד גבוהה ואוטומטים במידה רבה.

האוטומציה של כלים תהיה דרישה ב-20 ננו-מטר, והיא חשובה ביותר בעולם האנלוגי/מותאם, שם רוב התכנונים מבוצעים עדיין באופן ידני. יכולת אחת הדרושה היא מתודולוגיית אב-טיפוס אנלוגית מהירה המונחית על-ידי כוונת התכנון, ומודרכת על-ידי הערכות פרזיטיות לפני התסדיר בשלב מוקדם בתהליך התכנון. חיסכון עצום במחזורי התכנון אפשרי כאשר הוא משולב עם סגירה בתוך התכנון.

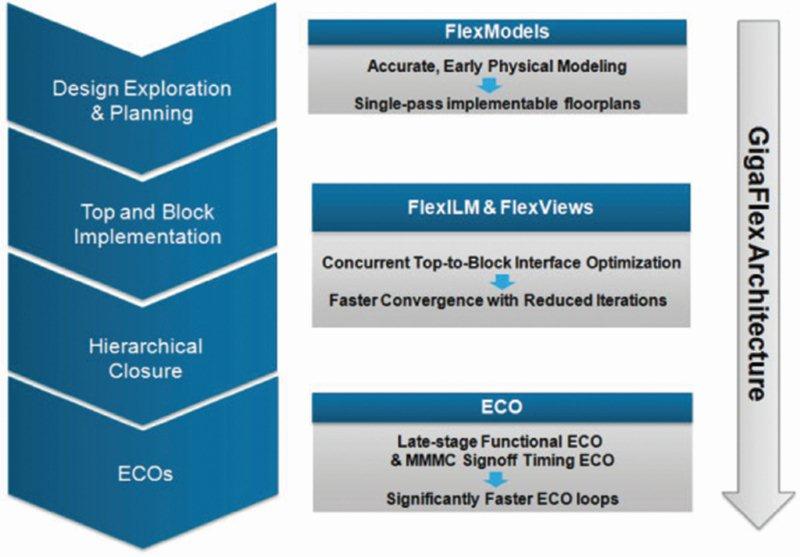

בתכנון דיגיטלי ושל מערכות-Soc טכניקת מידול גמישה צריכה לתמוך ברמות שונות של הפשטה, ולספק בדיוק את כמות הפרטים הנכונה עבור כל מטלה. מודלים המשמשים לחקירה ותכנון, לדוגמה, לא זקוקים לרמת הפרטים הדרושה עבור מימוש חלקי השבב או הסגירה ההירארכית. איור 3 מראה כיצד טכנולוגיית ההפשטה Cadence®GigaFlex מספקת גישת מידול גמישה עבור תכנוני 20 ננו-מטר גדולים.

גישה סידרתית, באמצעות כלים נקודתיים, לא תעבוד ב-20 ננו-מטר. מאחר וקיימות כל כך הרבה תלויות הדדיות, דרוש תהליך משולב קצה-אל-קצה. יש לשקול את כל ההשפעות כגון הדפס כפול, תזמונים ו-LDE מראש בתהליך התכנון ועל הכלים להבינן החל מאפיון IP ועד שלב הסגירה.

מורכבות תכנון ה-20 ננו-מטר דורשת סגירה במהלך שלבי התכנון. המשמעות היא שמנועים “באיכות סגירה” עבור המיקום, החיווט, התכנון לייצוריות (DFM) ניתוח תזמון ואיכות האות (signal integrity) (בין היתר) בודקים את העבודה שנעשתה בטרם ממשיכים הלאה. דבר זה אינו מחליף בהכרח את הרצת הבדיקה הסופית, אך גורם להרבה פחות עבודה כאשר המתכנן מגיע אליה וגורם לקיצור משמעותי של משך זמן התכנון.

לבסוף, תהליך של “מניעה, ניתוח, אופטימיזציה ” הוא קריטי. ניתן לחסוך הרבה שגיאות בעזרת תכנון מונחה-אילוצים, מיקום ער ל-LDE, מיקום וחיווט ער-לצבעים וסגירה תוך כדי מימוש. האנליזה צריכה לטפל בתריסרי נקודות עבודה שהמתכננים יפגשו ב-20 ננו-מטר, ולעשות זאת במהירות. בעזרת מניעה וניתוח, שלב האופטימיזציה הוא קל עם יחסית מעט שגיאות שיש לתקן.

אופטימיזציית PPA

בו-זמנית

שבבי 20 ננו-מטר לא יהיו רק גדולים. לשבבי 20 ננו-מטר רבים יהיו ביצועים בגיגה-הרצים, סכמות שעון מורכבות ואזורי מתחים שונים. כל דבר משפיע על כל דבר אחר, ויש לקחת בחשבון הספק, ביצועים ושטח (power, performance and area PPA) בו-זמנית. יכולת אחת אשר תידרש היא מתודולוגית אופטימיזציה באמצעות ליבות-מרובות אשר פועלת לאורך תהליך התכנון הפיסיקאלי של ה-IC.

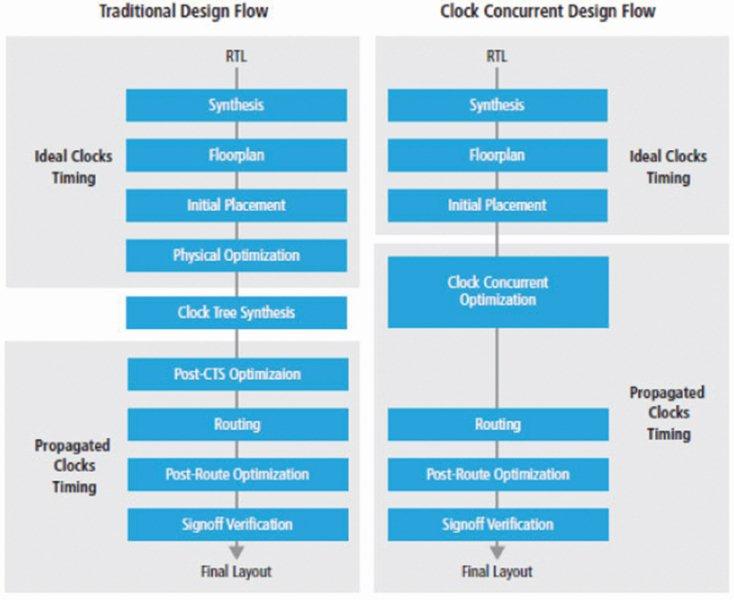

אחד השטחים המחייבים אופטימיזצייה בו-זמנית הוא השעון. הגישה המסורתית לסנתוז עץ השעון (clock tree synthesis – CTS) מתמקדת במזעור סטיית השעון, ומבצעת CTS בנפרד מאופטימיזציה פיזיקאלית. אופטימיזצית שעון בו זמנית היא טכנולוגיה חדשה, אשר מבצעת את סינטזת השעון מונחית על ידי חלונות זמן בניגוד ל סינטזת שעון מונחית ע”י סטיית השעון, ואשר מאחדת את התהליך עם אופטימיזציה פיסיקאלית (איור 4). התוצאות הנצפות כוללות הפחתת הספק עץ השעון ב-30%, צמצום שטח עץ השעון ב-30% ושיפורים בביצועי השבב ב-100 מגה-הרץ עבור שבב גיגה-הרצי עם מעבדי ARM.

בשוק הצריכה, שבבי 20 ננו-מטר מחוייבים לביצועים גבוהים והספק נמוך, ובכך מגבירים את המורכבות ומציבים קונפליקטים קשים. שבבי 20 ננו-מטר רבים ישתמשו בטכניקות של ניהול הספק מתקדמות כגון איי מתחים מרובים וכיבוי הספקות. ניהול משטר ההספקים ואיכות האותות יידרשו גם כן בשבבים, מארזים וכרטיסים, ויעשו את התכנון המשותף IC/מארז חשוב יותר מאי-פעם.

פיסות רבות של 20 ננו-מטר יעברו אולי למארזי 2.5D (חוצץ סיליקון) ו-3D (פיסה בערימה עם via דרך-סיליקון). תהליך תכנון דיגיטלי ואנלוגי תומך ב-D3 ויכולת תכנון יחד IC/מארז יידרשו כדי לעשות את ערימת הפיסות מעשית ומשתלמת.

סיכום

תכנון 20 ננו-מטר מציב אתגרים בשלושה תחומים: יכולות הייצור והשונות בסיליקון, מורכבות תכנון בקנה מידה גיגה ואופטימיזציית PPA בו-זמנית. אולם, ניתן להתגבר על אתגרים אלו באמצעות הכלים והשיטות הנכונים. ואף על פי ש20 ננו-מטר תחייב גישות חדשות לתכנון וייצוריות ICs, השינויים יביאו לשיפורים ארוכי-טווח בתהליך תכנון הסיליקון.

אוסף כלים-נקודתיים אנלוגיים ודיגיטליים ייסוגו לטובת פתרונות קצה-לקצה משולבים, המסוגלים לנהל את הקונפליקטים והתלויות ההדדיות המורכבות,הפשרות והאופטימיזציות ההכרחיים ב-20 ננו-מטר. והגישה הבלתי-אפשרית “תקן זאת בסגירה” תוחלף לתהליך ה-“מניעה, ניתוח, אופטימיזציה “הנדון במאמר זה. וזה לא יקרה בעתיד הרחוק. תהליך כזה הוא כבר חלק מפתרון תכנון שלם, מוכן-ל-20 ננו-מטר, מותאם/אנלוגי ודיגיטלי הזמין כבר ב-Cadence.

סימוכין

[1] “Clock Concurrent Optimization Reshapes IC Physical Design Flow”, Chip Design Magazine

[2]

3D-ICs With TSVs – Design Challenges and Requirements, white paper,cadence.com

Samta Bansal and Richard Goering, Cadence